# 4046B

# MICROPOWER PHASE-LOCKED LOOP

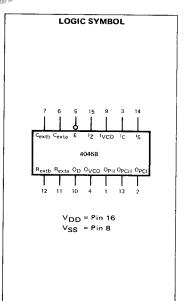

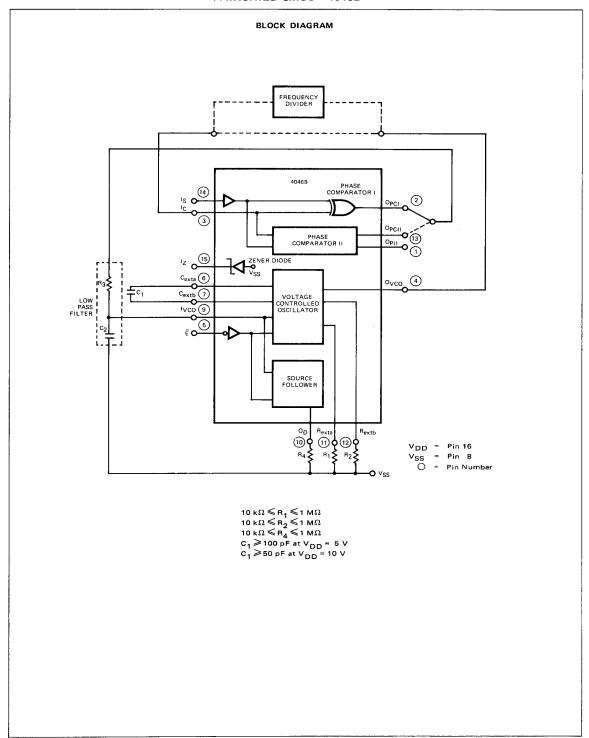

DESCRIPTION — The 4046B is a Micropower Phase-Locked Loop consisting of a low power linear Voltage-Controlled Oscillator, a Source Follower Circuit, two different Phase Comparators, and a Zener diode. The Voltage-Controlled Oscillator has two External Capacitor connections (Cexta, Cextb), two External Resistor connections (Rexta, Rextb), a Voltage-Controlled Oscillator Input (IVCQ) and a Voltage-Controlled Oscillator Output (OVCQ). The Source Follower Circuit provides a Demodulated Output (Op) from the Voltage-Controlled Oscillator. An active LOW Enable Input (E) common to both the Voltage-Controlled Oscillator and the Source Follower Circuit is also provided. Phase Comparator I and Phase Comparator II have common Signal (Is) and Comparator (Ic) Inputs and separate outputs; Phase Comparator I Output (OPCI), Phase Comparator II Output (OPCII), and Phase Pulse Output (OPII). An input to the Zener diode (Iz) is also provided.

The Voltage-Controlled Oscillator requires one external capacitor ( $C_1$ ) and one external resistor ( $R_1$ ) to determine operational frequency range. A second external resistor ( $R_2$ ) may be used to allow frequency offset. External resistor  $R_3$  and external capacitor  $C_2$  combined serve as a low pass filter to the Voltage-Controlled Oscillator Input ( $I_{VCO}$ ). Output  $O_D$  is provided to avoid loading the low pass filter. External resistor  $R_4$  is required if this output is utilized.  $O_D$  must be left open when not utilized. The output from the Voltage-Controlled Oscillator ( $O_{VCO}$ ) may be connected directly or indirectly through CMOS frequency dividers (i.e., the 40188, 40208, 40228, 40248, 4029B, 40408, 45188, 45208, 401608, 401618, 401628, 401638, 40192B or 401938) to the Comparator Input ( $I_C$ ). With the Enable Input (E) HIGH both the Voltage-Controlled Oscillator and the Source Follower Circuit are OFF to minimize power consumption. With E LOW, both are enabled.

For direct-coupling between  $O_{VCO}$  and  $I_{C}$ , the voltage swing at the Voltage-Controlled Oscillator Output  $(O_{VCO})$  must be within standard CMOS logic levels  $(V_{OH} \geqslant 0.7 \times V_{DD})$  and  $V_{OL} \leqslant 0.3 \times V_{DD}$ ; otherwise the signal from  $O_{VCO}$  must be capacitively coupled to the Signal Input  $(I_S)$ .

Phase Comparator I is an Exclusive OR circuit (I<sub>C</sub>  $\oplus$  I<sub>S</sub>). I<sub>C</sub> and I<sub>S</sub> must have 50% duty cycles to maximize lock range. When the Output of Phase Comparator I (Opcl) is connected back to the Voltage-Controlled Oscillator through the low pass filter network, an averaged voltage to I<sub>VCO</sub> forces oscillation at a center frequency.

Phase Comparator II is an edge-triggered digital memory network with four flip-flop stages, associated control circuitry and a 3-state output. Phase Comparator II triggers on LOW-to-HIGH transitions at the Signal (Ig) and Comparator (Ic) Inputs and is independent of duty cycle at these inputs. The Output of Phase Comparator II (OpcII) provides voltage levels and duty cycles corresponding to frequency and phase differentials between Ic and Ig. When OpcII is connected to the Voltage-Controlled Oscillator Input (I<sub>V</sub>Co) through the low pass filter network, a corresponding voltage across capacitor C<sub>2</sub> is adjusted until the Signal (Ig) and Comparator (Ic) Inputs are equal in both frequency and phase. At this point Phase Comparator II maintains a constant voltage across Capacitor C<sub>2</sub>. When this stability has been established, the Phase Pulse Output (OpII) is HIGH indicating a locked condition. Power dissipation in the low pass filter is reduced when Phase Comparator II is used.

A zener diode is provided for regulating the power supply voltage, if necessary.

- VERY LOW POWER CONSUMTPION

- HIGH VCO LINEARITY, 1% TYPICAL

- CHOICE OF 2-PHASE COMPARATORS

- ENABLE INPUT (ACTIVE LOW) FOR LOW POWER DISSIPATION IN STANDBY MODE

- ON-CHIP ZENER DIODE FOR SUPPLY REGULATION

- VCO FREQUENCY DRIFT WITH TEMPERATURE = 0.04% / °C TYPICAL AT VDD = 10 V

### **PIN NAMES**

IZ Zener Diode Input IS Signal Input IC Comparator Input

IVCO Voltage-Controlled Oscillator Input

E Enable Input (Active LOW)

Cexta, Cextb External Capacitor Connections

Rextar, Rextb External Resistor Connections

OPCI Phase Comparator I Output

OPCII Phase Comparator II Output

OPII Phase Pulse Output

OD Demodulator Output

OVCO Voltage-Controlled Oscillator Output

#### CONNECTION DIAGRAM DIP (TOP VIEW)

NOTE:

The Flatpak version has the same pinouts (Connection Diagram) as the Dual In-line Package.

## FAIRCHILD CMOS • 4046B

**FUNCTIONAL DESCRIPTION** — The 4046B, Micropower Phase-Locked Loop consists of a low power linear Voltage-Controlled Oscillator (VCO), a Source Follower circuit (SF), two Phase Comparators (PCI and PCII) and a Zener diode.

#### **VOLTAGE-CONTROLLED OSCILLATOR**

The VCO requires one external capacitor (C<sub>1</sub>) and one external resistor (R<sub>1</sub>) to determine operational frequency range. External resistor R<sub>2</sub> is used to allow for frequency offset, if required. It is recommended that R<sub>1</sub> and R<sub>2</sub> have a value between 10 k $\Omega$  and 1 M $\Omega$ . At V<sub>DD</sub> = 5 V, C<sub>1</sub> should be greater than or equal to 100 pF, and at V<sub>DD</sub> = 10 V, C<sub>1</sub> should be greater than or equal to 50 pF.

External resistor R<sub>3</sub> and external capacitor C<sub>2</sub> combined serve as a low-pass filter to the Voltage-Controlled Oscillator Input (I<sub>VCO</sub>). The user is allowed a wide range of resistor-to-capacitor ratios for R<sub>3</sub> and C<sub>2</sub> because of the high imput impedance at I<sub>VCO</sub> (approximately 1012  $\Omega$ ).

To avoid loading of the low-pass filter, the Demodulator Output  $(O_D)$  should be connected through external resistor  $R_4$  as shown in the Block Diagram. It is recommended that  $R_4$  have a value between  $10 \text{ k}\Omega$  and  $1 \text{ M}\Omega$ . If the  $O_D$  output is not utilized it must be left open.

The Voltage-Controlled Oscillator Output ( $O_{VCO}$ ) provides a 0.3  $V_{DD}$  to 0.7  $V_{DD}$  output voltage swing and may be connected to the Comparator Input ( $I_C$ ).  $O_{VCO}$  may, also be connected indirectly to  $I_C$  via CMOS frequency dividers (i.e., the 4018B, 4022B, 4029B, 4040B, 4518B, 4520B, 40160B, 40161B, 40162B, 40163B, 40192B, and 40193B.)

An Enable Input  $(\overline{E})$  to the VCO and SF is provided for minimum stand-by power dissipation. With the  $\overline{E}$  Input HIGH both the VCO and the SF are OFF. With  $\overline{E}$  LOW, both are enabled.

#### PHASE COMPARATORS

For direct-coupling between OVCO and IC, the voltage swing at OVCO must be within standard CMOS logic levels ( $V_{OH} > 0.7 V_{DD}$  and  $V_{OL} < 0.3 V_{DD}$ ); otherwise the signal from OVCO must be capacitively coupled to the self-biasing amplifier at the IS Input.

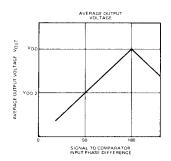

Phase Comparator I is an Exclusive OR circuit ( $I_C \oplus I_S$ ). For maximum lock range, inputs to  $I_C$  and  $I_S$  must have 50% duty cycles. (Lock range, 2f<sub>L</sub>, is defined as that frequency range of input signals upon which the 4046B will stay locked from an initial locked condition). With no signal or noise input, Phase Comparator I provides an average output voltage equal to  $V_DD/2$  at the  $O_{PC}$  Output. This average output voltage is supplied to the  $I_{VCO}$  Input through the low-pass filter, which in turn forces the VCO to oscillate at a center frequency ( $I_C$ ).

Capture range 2f<sub>C</sub>, is defined as that frequency range of input signals upon which the 4046B will lock from an initial unlocked condition. Capture range for PCI is directly dependent upon the characteristics of the low-pass filter network and may be as great as the lock range. Thus, PCI allows the user a phase-locked loop system which will remain in a locked condition despite high amounts of noise in the input signal.

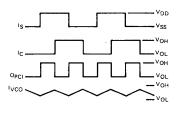

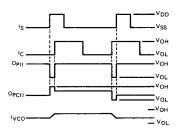

It should be noted that with the use of PCI the system may lock onto input signals with frequencies that are near harmonics to the center frequency of the VCO. It should further be noted that the phase angle between the I<sub>C</sub> and I<sub>S</sub> Inputs will vary between 0° and 180°. At the center frequency the phase angle is 90°. Figure 2 illustrates a typical Phase Angle versus Average Output Voltage response characteristic for PCI. Figure 3 illustrates the typical waveforms for a phase-locked loop system employing PCI and locked at a center frequency.

Phase Comparator II is edge-triggered digital memory network with four flip-flop stages, associated control circuitry and a 3-state output, controlled internally. PCII triggers on LOW-to-HIGH transitions at the Signal (Ig) and Comparator (IC) Inputs and is independent of duty cycle at these inputs. If the input frequency at Ig is higher than the input frequency at Ig, the p-channel output transistor at OpcII is turned "ON" continuously, pulling the output (OpcII) toward VDD. If the input frequency at Ig is higher than the input frequency at Ig, the n-channel output transistor at OpcII is turned "ON" continuously, pulling the output toward Vgs. If the input frequencies at Ig and Ig are equal, but Ig lags Ig in phase, the n-channel output transistor is turned "ON" for a period of time corresponding to the phase difference. If the input frequencies at Ig and Ig are equal, but Ig lags Ig in phase, the p-channel output transistor is turned "ON" for a period of time corresponding to the phase difference. Thus, over a period of time the voltage at capacitor C2 is adjusted until the Ig and Ig input signals are of the same frequency and phase. Once this stability is reached, both p- and n-channel output transistors at OpcII are "OFF". OpcII becomes an open circuit holding the voltage across C2 constant.

Once this stability is attained, the Phase Pulse Output (Op11) is HIGH indicating a locked condition.

With PCII no phase difference is present between I<sub>C</sub> and I<sub>S</sub> over the entire VCO frequency range. Furthermore, since the 3-state Phase Comparator II Output (Opc<sub>II</sub>) is mostly in the "OFF" condition, power dissipation through the low-pass filter is minimized. It should also be noted that  $2f_C = 2f_L$  independent of the filter network in a phase-locked loop utilizing PCII. Figure 4 shows typical waveforms for a phase-locked loop system employing Phase Comparator II and locked at a center frequency.

Fig. 2 CHARACTERISTICS OF PHASE COMPARATOR I AT THE LOW PASS FILTER OUTPUT.

Fig. 3 A PLL SYSTEM USING PHASE COMPARATOR I.

Fig. 4 A PLL SYSTEM USING PHASE COMPARATOR II

Fig. 5 TYPICAL LOW-PASS FILTERS.

Fig. 6 DESIGN INFORMATION.

| Characteristic                                                                             | Using Phase Comparator 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Using Phase Comparator 2                                             |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| No signal on input I <sub>S</sub>                                                          | VCO in PLL system adjusts to center frequency $(f_0)$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VCO in PLL system adjusts to minimum fre quency (f <sub>min</sub> ). |  |  |  |  |  |  |  |  |

| Phase angle between I <sub>S</sub> and I <sub>C</sub>                                      | 90° at center frequency (f <sub>0</sub> ), approaching 0° and 180° at ends of lock range (2f <sub>L</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                           | Always 0° in lock (positive rising edges).                           |  |  |  |  |  |  |  |  |

| Locks on harmonics of center frequency.                                                    | Yes No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                      |  |  |  |  |  |  |  |  |

| Signal input noise rejection.                                                              | HIGH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LOW                                                                  |  |  |  |  |  |  |  |  |

| Lock frequency range (2fL).                                                                | The frequency range of the input signal on which the loop will stay locked if it was initially in lock. $2f_L = \text{full VCO frequency range} = f_{\text{max}} - f_{\text{min}}$ .                                                                                                                                                                                                                                                                                                                                   |                                                                      |  |  |  |  |  |  |  |  |

| Capture frequency range (2f <sub>C</sub> ).                                                | The frequency range of the input signal on which the loop will lock if it was initially out of lock.                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                      |  |  |  |  |  |  |  |  |

|                                                                                            | Depends on low-pass filter characteristics (Figure 5) $f_C \le f_L$                                                                                                                                                                                                                                                                                                                                                                                                                                                    | f <sub>C</sub> = f <sub>L</sub>                                      |  |  |  |  |  |  |  |  |

| Center frequency (f <sub>0</sub> ).                                                        | The frequency of O <sub>VCO</sub> when I <sub>VCO</sub> = 1/2 V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                      |  |  |  |  |  |  |  |  |

| OVCO frequency (f).  NOTE: The information presented here is meant only as a design guide. | $f \approx \frac{K \left[ \frac{I_{VCO} - 1.65}{R_1} + \frac{V_{DD} - 1.35}{R_2} \right]}{(C_1 + 32) (V_{DD} + 1.6)}  \text{MHz (a}$ where: $V_{DD} \text{ in } V; 5 \ V \leqslant V_{DD} \leqslant 15 \ V$ $I_{VCO} \text{ in } V; 1.65 \ V \leqslant I_{VCO} \leqslant (V_{DD} - 1.35 \ V)$ $R_1 \text{ and } R_2 \text{ in } M\Omega; R_1, R_2 \geqslant 0.005 \ M\Omega$ $C_1 \text{ in } pF; C_1 \geqslant 50 \ pF$ $K = 0.95 \ @ \ V_{DD} = 5 \ V$ $= 0.95 \ @ \ V_{DD} = 10 \ V$ $= 1.08 \ @ \ V_{DD} = 15 \ V$ | t 25°C)  8 fmax  fmin  1/2 VDD  VDD                                  |  |  |  |  |  |  |  |  |

# FAIRCHILD CMOS • 4046B

UNITS

TEMP

TEST CONDITIONS

**DC CHARACTERISTICS:**  $V_{DD}$  as shown,  $V_{SS} = 0$  V (Note 1)

PARAMETER

SYMBOL

| ***            | CAL CHARAC                      |                                                                    |                                                                                  |    |      | 33              |         | <u> </u> |                 | TC  |                     |                  |                   | т     | T                            |

|----------------|---------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------|----|------|-----------------|---------|----------|-----------------|-----|---------------------|------------------|-------------------|-------|------------------------------|

| SYMBOL         | PARAMETER                       |                                                                    | LIMITS   V <sub>DD</sub> = 5 V   V <sub>DD</sub> = 10 V   V <sub>DD</sub> = 15 V |    |      |                 |         |          |                 |     | 5 V                 | UNITS            | TEST CONDITION    |       |                              |

|                |                                 |                                                                    | MIN                                                                              |    | MAX  | MIN             |         | MAX      | MIN             | TYP |                     | 1                | TEO CONDITION     |       |                              |

|                | Propagation [                   | Delay                                                              |                                                                                  |    |      |                 |         |          |                 |     |                     |                  |                   |       | C <sub>L</sub> = 50 pF       |

| TLH            | Output Transition               |                                                                    |                                                                                  |    |      | 72<br>72        | ĺ       |          | 48              |     |                     | 38               |                   | ns    | R <sub>L</sub> = 200 kΩ      |

| THL            | Time                            |                                                                    |                                                                                  |    |      |                 |         | 48       | i               |     | 38                  | Input Transition |                   |       |                              |

| PHASE CO       | <br> <br>  DMPARATORS           | <b>.</b>                                                           |                                                                                  |    |      | L               | ļ       |          | L               | L   |                     |                  |                   | l     | Times ≤ 20 ns                |

| RIN            | Input                           |                                                                    | s                                                                                |    | T    | 200             | l       |          | 400             |     |                     | 700              |                   |       |                              |

| .114           | Resistance                      |                                                                    | l <sub>C</sub>                                                                   |    |      | 10 <sup>6</sup> |         |          | 10 <sup>6</sup> |     |                     | 106              | -                 | MΩ    |                              |

| VIN            | AC Coupled I                    |                                                                    |                                                                                  |    |      | 200             |         |          | 400             |     |                     | 700              |                   | mV    |                              |

|                | Sensitivity for<br>DC Coupled I |                                                                    | <del></del>                                                                      |    |      |                 |         | L        |                 | L   |                     |                  |                   | p-p   |                              |

|                | Sensitivity for                 | See Note 1 for V <sub>IH</sub> and V <sub>IL</sub> Characteristics |                                                                                  |    |      |                 |         |          |                 | Ì   |                     |                  |                   |       |                              |

| VOLTAGE        | CONTROLLE                       |                                                                    | ILLATE                                                                           | ER | J    |                 |         |          |                 |     |                     |                  |                   |       |                              |

|                |                                 |                                                                    |                                                                                  |    |      | 0.12            |         |          | 0.04            |     |                     | 0.015            |                   |       | No Frequency                 |

| 1              |                                 |                                                                    |                                                                                  |    |      | 0.12            |         |          | 0.08            | Ì   |                     | 0.03             |                   | %/°c  | Offset, f <sub>min</sub> = 0 |

|                | Temperature-                    |                                                                    |                                                                                  |    |      |                 |         |          |                 |     |                     | 0.00             |                   |       | See Note 3                   |

|                | Frequency Stability             |                                                                    |                                                                                  |    | 0.06 |                 |         | 0.05     |                 |     | 0.03                |                  | Frequency Offset, |       |                              |

|                |                                 |                                                                    | 0.12                                                                             |    |      | 0.10            |         |          | 0.06            |     | f <sub>min</sub> ≠0 |                  |                   |       |                              |

|                | Linearity                       |                                                                    |                                                                                  |    | -    | 1               |         |          | 1               |     |                     | 1                |                   | %     | See Note 4<br>See Note 2     |

|                | Output Duty                     |                                                                    |                                                                                  |    |      |                 |         |          |                 |     |                     |                  |                   |       | O <sub>VCO</sub> tied to     |

|                | Cycle                           |                                                                    |                                                                                  |    |      | 50              |         |          | 50              |     |                     | 50               |                   | %     | Ic                           |

| RIN            | Input Resistar                  | nce                                                                |                                                                                  |    |      | 10 <sup>6</sup> |         |          | 106             |     |                     | 10 <sup>6</sup>  |                   | МΩ    |                              |

|                | to IVCO                         |                                                                    |                                                                                  |    |      |                 |         |          |                 |     |                     |                  |                   | 10,43 |                              |

| max            | Maximum<br>Operating Fre        | diency                                                             |                                                                                  |    |      | 0.9             |         |          | 1.7             |     |                     | 2.3              |                   | MIIz  | See Note 6                   |

| OURCE I        | FOLLOWER                        | quency                                                             |                                                                                  | ·  |      |                 |         |          |                 |     | i                   |                  |                   |       |                              |

|                | Offset Voltage                  |                                                                    |                                                                                  |    |      |                 | Ī       |          |                 |     |                     | Т                | .=                |       |                              |

| v <sub>D</sub> | at O <sub>D</sub>               | •                                                                  |                                                                                  |    |      | 1.65            |         |          | 1.65            |     |                     | 1.65             |                   | V     | $R_4 > 10 \text{ k}\Omega$   |

|                | Linearity                       |                                                                    |                                                                                  |    |      | 0.1             |         |          | 0.6             |     |                     | 0.8              |                   | %     | See Note 5                   |

| ZENER DI       | ODE                             |                                                                    |                                                                                  |    | L    |                 | <u></u> | !        |                 |     |                     |                  |                   |       |                              |

| /z             | Zener Voltage                   |                                                                    |                                                                                  |    |      | 7               |         | Ī        | 7               |     |                     | 7                |                   | V     | I <sub>Z</sub> = 50 μA       |

|                | Zener Dynami                    | ic                                                                 |                                                                                  |    |      | 100             |         |          | 100             |     |                     | 100              |                   |       |                              |

| <sup>R</sup> Z | Resistance                      |                                                                    |                                                                                  |    |      | 100             |         |          | 100             |     |                     | 100              |                   | Ω     | $I_Z = 1 \text{ mA}$         |