**User's Manual**

# VR10000<sup>™</sup>, VR12000<sup>™</sup>

64-bit Microprocessor

μ**PD30700** μ**PD30700L** μ**PD30710**

Document No. U10278EJ3V0UM00 (3rd edition) Date Published May 1998 N CP(K)

NEC Corporation 1995

MIPS Technologies, Inc. 1994

Printed in Japan

[MEMO]

# **Summary of Contents**

| Chapter 1  | Introduction to the R10000 Processor  | 21          |

|------------|---------------------------------------|-------------|

| Chapter 2  | System Configurations                 | 53          |

| Chapter 3  | Interface Signal Descriptions         | 57          |

| Chapter 4  | Cache Organization and Coherency      | 65          |

| Chapter 5  | Secondary Cache Interface             | 81          |

| Chapter 6  | System Interface Operations           | <b></b> 101 |

| Chapter 7  | Clock Signals                         | <b></b> 177 |

| Chapter 8  | Initialization                        | <b></b> 181 |

| Chapter 9  | Error Protection and Handling         | <b></b> 191 |

| Chapter 10 | JTAG Interface Operation              | 211         |

| Chapter 11 | Electrical Specifications             | <b></b> 217 |

| Chapter 12 | Packaging                             | <b></b> 227 |

| Chapter 13 | Coprocessor 0                         | <b></b> 241 |

| Chapter 14 | Floating-Point Unit                   | <b></b> 291 |

| Chapter 15 | Memory Management                     | <b></b> 303 |

| Chapter 16 | CPU Exceptions                        | <b></b> 319 |

| Chapter 17 | Cache Test Mode                       | <b></b> 347 |

| Appendix A | Glossary                              | <b></b> 357 |

| Appendix B | Differences between R10000 and R12000 | <b></b> 365 |

| Appendix C | Index                                 | <b></b> 377 |

#### NOTES FOR CMOS DEVICES

#### **1** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### **(2)** HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

VR3000,VR4200,VR4300,VR4400,VR5000,VR10000,VR12000,and,VR-Series are trademarks of NEC Corporation. RISCompiler, RISC/os, R2000,R3000,R4000,and R6000 are trademarks of MIPS Computer Systems Inc. MIPS,R4200,R4300,R4400,R8000, and R10000 are trademarks of MIPS Technologies, Inc. UNIX is a registered trademark in the United States and other countries, licensed exclusively through X/Open Company, Ltd. The export of this product from Japan is prohibited without governmental license. To export or re-export this product from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

Exporting this product or equipment that includes this product may require a governmental license from the U.S.A. for some countries because this product utilizes technologies limited by the export control regulations of the U.S.A.

#### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

[MEMO]

# RegionalInformation

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- Ordering information

- Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

| NEC Electronics Inc. (U.S.)<br>Santa Clara, California<br>Tel: 408-588-6000<br>800-366-9782<br>Fax: 408-588-6130<br>800-729-9288 | NEC Electronics (Germany) GmbH<br>Benelux Office<br>Eindhoven, The Netherlands<br>Tel: 040-2445845<br>Fax: 040-2444580 | NEC Electronics Hong Kong Ltd.<br>Hong Kong<br>Tel: 2886-9318<br>Fax: 2886-9022/9044<br>NEC Electronics Hong Kong Ltd.                      |

|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| NEC Electronics (Germany) GmbH<br>Duesseldorf, Germany<br>Tel: 0211-65 03 02<br>Fax: 0211-65 03 490                              | NEC Electronics (France) S.A.<br>Velizy-Villacoublay, France<br>Tel: 01-30-67 58 00<br>Fax: 01-30-67 58 99             | Seoul Branch<br>Seoul, Korea<br>Tel: 02-528-0303<br>Fax: 02-528-4411                                                                        |

| <b>NEC Electronics (UK) Ltd.</b><br>Milton Keynes, UK<br>Tel: 01908-691-133<br>Fax: 01908-670-290                                | NEC Electronics (France) S.A.<br>Spain Office<br>Madrid, Spain<br>Tel: 01-504-2787<br>Fax: 01-504-2860                 | NEC Electronics Singapore Pte. Ltd.<br>United Square, Singapore 1130<br>Tel: 65-253-8311<br>Fax: 65-250-3583<br>NEC Electronics Taiwan Ltd. |

| NEC Electronics Italiana s.r.1.<br>Milano, Italy<br>Tel: 02-66 75 41<br>Fax: 02-66 75 42 99                                      | NEC Electronics (Germany) GmbH<br>Scandinavia Office<br>Taeby, Sweden<br>Tel: 08-63 80 820<br>Fax: 08-63 80 388        | Taipei, Taiwan<br>Tel: 02-719-2377<br>Fax: 02-719-5951<br>NEC do Brasil S.A.<br>Cumbica-Guarulhos-SP, Brasil<br>Tel: 011-6465-6810          |

Fax: 011-6465-6829

| Page                                                                                    | Description                                                                                   |  |  |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|

| p.26 Addition of Load/store dependency is speculatively ignored (R12000) in 1.3 What    |                                                                                               |  |  |

|                                                                                         | R10000 Microprocessor?                                                                        |  |  |

| p.29                                                                                    | Addition of Increase in pre-decode buffering (R12000) in 1.3 What is an R10000                |  |  |

|                                                                                         | Microprocessor?                                                                               |  |  |

| p.30                                                                                    | Addition of Branch Target Address Cache (R12000) in 1.3 What is an R10000                     |  |  |

|                                                                                         | Microprocessor?                                                                               |  |  |

| p.31                                                                                    | Addition of Additional cycles for System Interface Transactions (R12000) in 1.3 What is an    |  |  |

|                                                                                         | R10000 Microprocessor?                                                                        |  |  |

| p.32                                                                                    | Addition of FP and Integer-Queue Issue Policy in 1.4 Instruction Queues                       |  |  |

| p.32 Addition of Address calculation for load/store instructions uses integer queue (RI |                                                                                               |  |  |

|                                                                                         | 1.4 Instruction Queues                                                                        |  |  |

| p.63                                                                                    | Addition of <r12000> Changed Spare (1,3) pins to NC (No Connection) in Table3-4 Test</r12000> |  |  |

|                                                                                         | Interface Signals                                                                             |  |  |

| p.69                                                                                    | Addition of DCache set locking relaxed (R12000) in 4.2 Primary Data Cache                     |  |  |

| p.73                                                                                    | Addition of <b><r12000></r12000></b> in <b>4.3 Secondary Cache</b>                            |  |  |

| p.87                                                                                    | Addition of Increased the Way Prediction Table (MRU table) to 16K single-bit entries,         |  |  |

|                                                                                         | Direct Cache Test Mode in 5.4 Secondary Cache Way Prediction Table                            |  |  |

| p.187                                                                                   | Modification of description in Table 8-1 Mode Bits                                            |  |  |

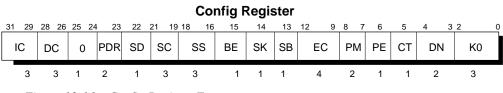

| p.262                                                                                   | Modification of description in Table 13-15 Config Register Field Definitions                  |  |  |

| p.262                                                                                   | Modification of description in Figure 13-16 Config Register Format                            |  |  |

| p.269                                                                                   | Addition of description in <b>13.19 Diagnostic Register</b> ( <b>22</b> )                     |  |  |

| p.293                                                                                   | Addition of Eliminate traps for Denorm/NaN FP inputs (R12000) in 14.2 Floating-Point Unit     |  |  |

|                                                                                         | Control                                                                                       |  |  |

| p.357                                                                                   | Addition of Appendix A Glossary                                                               |  |  |

| p.365                                                                                   | Addition of Appendix B Differences between R10000 and R12000                                  |  |  |

The mark  $\bigstar$  shows major revised points.

## PREFACE

| Readers                 | This manual targets users who intends to understand the functions of the VR10000 and VR12000,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                         | and to design application systems using this microprocessor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Purpose                 | This manual introduces the architecture and hardware functions of the VR10000, VR12000 to users, following the organization described below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Organization            | <ul> <li>This manual consists of the following contents:</li> <li>Introduction</li> <li>Cache</li> <li>Hardware</li> <li>Coprocessor 0</li> <li>Floating point unit</li> <li>Memory management system</li> <li>Exception processing</li> <li>Instruction set details</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| How to read this manual | It is assumed that the reader of this manual has general knowledge in the fields of electric engineering, logic circuits, and microcomputers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|                         | <ul> <li>The R3000<sup>TM</sup> in this manual represents the VR3000<sup>TM</sup>.</li> <li>The R4200<sup>TM</sup> in this manual represents the VR4200<sup>TM</sup>.</li> <li>The R4300<sup>TM</sup> in this manual represents the VR4300<sup>TM</sup>.</li> <li>The R4400<sup>TM</sup> in this manual represents the VR4400<sup>TM</sup>.</li> <li>The R10000<sup>TM</sup> in this manual represents the VR10000<sup>TM</sup>.</li> <li>The R12000<sup>TM</sup> in this manual represents the VR10000<sup>TM</sup>.</li> <li>To learn about detailed function of a specific instruction.</li> <li>→ Read Chapter 14 Floating-Point Unit, Chapter 16 CPU Exceptions, or refer to VR5000, VR10000 User's Manual INSTRUCTION which is separately available.</li> <li>To learn about the overall functions of the VR10000 and VR12000</li> <li>→ Read this manual in sequential order.</li> <li>To learn about electrical specifications,</li> <li>→ Refer to Data Sheet which is separately available.</li> <li>Unless otherwise specified, the R10000 is treated as the representative model throughout this document.</li> </ul> |  |  |

| Legend                  | Data significance:Higher on left and lower on rightActive low:XXX*Numeric representation:binary XXXX or XXXX2decimal XXXXhexadecimal 0xXXXXImportant informationUnderlined                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Related Documents       | The related documents indicated here may include preliminary version. However, preliminary versions are not marked as such.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                         | Data sheet<br>VR10000, VR12000 Data Sheet To be issued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                         | User's Manual<br>VR5000, VR10000 User's Manual INSTRUCTION U12754E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

[MEMO]

## CONTENTS

## 1. Introduction to the R10000 Processor

| 1.1 | MIPS Instruction Set Architecture (ISA)                                     |    |

|-----|-----------------------------------------------------------------------------|----|

| 1.2 | What is a Superscalar Processor?                                            |    |

|     | Pipeline and Superpipeline Architecture                                     |    |

|     | Superscalar Architecture                                                    |    |

| 1.3 | What is an R10000 Microprocessor?                                           |    |

|     | R10000 Superscalar Pipeline                                                 |    |

|     | Instruction Queues                                                          |    |

|     | Execution Pipelines                                                         |    |

|     | Load/store dependency is speculatively ignored (R12000)                     |    |

|     | 64-bit Integer ALU Pipeline                                                 |    |

|     | Load/Store Pipeline                                                         |    |

|     | 64-bit Floating-Point Pipeline                                              |    |

|     | Functional Units                                                            |    |

|     | Increase in pre-decode buffering (R12000)                                   |    |

|     | Primary Instruction Cache (I-cache)                                         |    |

|     | Primary Data Cache (D-cache)                                                |    |

|     | Branch Target Address Cache (R12000)                                        |    |

|     | Instruction Decode And Rename Unit                                          |    |

|     | Branch Unit                                                                 |    |

|     | External Interfaces                                                         |    |

|     | Additional cycles for System Interface transactions (R12000)                |    |

| 1.4 | Instruction Queues                                                          |    |

| 1.4 | FP and Integer-Queue Issue Policy (R12000)                                  |    |

|     | Integer Queue Issue Foncy (K12000)                                          |    |

|     | Address calculation for load/store instructions uses integer queue (R12000) |    |

|     | Floating-Point Queue                                                        |    |

|     | Address Queue                                                               |    |

| 1.5 | Program Order and Dependencies                                              |    |

| 1.5 |                                                                             |    |

|     | Instruction Dependencies                                                    |    |

|     | Execution Order and Stalling                                                |    |

|     | Branch Prediction and Speculative Execution                                 |    |

|     | Resolving Operand Dependencies                                              |    |

|     | Resolving Exception Dependencies                                            |    |

|     | Strong Ordering                                                             |    |

| 1.6 | An Example of Strong Ordering                                               |    |

| 1.6 | R10000 Pipelines                                                            |    |

|     | Stage 1                                                                     |    |

|     | Stage 2                                                                     |    |

|     | Stage 3                                                                     |    |

|     | Stages 4-6                                                                  |    |

|     | Floating-Point Multiplier (3-stage Pipeline)                                |    |

|     | Floating-Point Divide and Square-Root Units                                 |    |

|     | Floating-Point Adder (3-stage Pipeline)                                     |    |

|     | Integer ALU1 (1-stage Pipeline)                                             |    |

|     | Integer ALU2 (1-stage Pipeline)                                             |    |

|     | Address Calculation and Translation in the TLB                              |    |

| 1.7 | Implications of R10000 Microarchitecture on Software                        |    |

|     | Superscalar Instruction Issue                                               |    |

|     | Speculative Execution                                                       |    |

|     | Side Effects of Speculative Execution                                       |    |

|     | Nonblocking Caches                                                          | 47 |

| 1.8 | Performance                              | 48 |

|-----|------------------------------------------|----|

|     | User Instruction Latency and Repeat Rate | 49 |

|     | Other Performance Issues                 |    |

|     | Cache Performance                        |    |

|     |                                          |    |

# 2. System Configurations

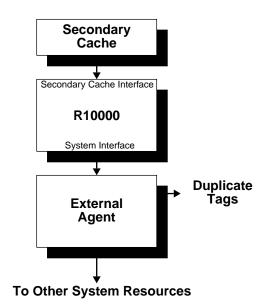

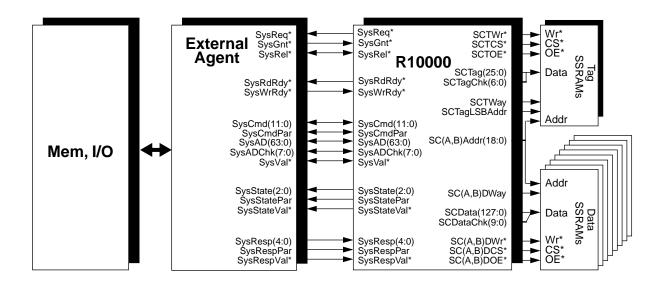

| 2.1 | Uniprocessor Systems                                   | 54 |

|-----|--------------------------------------------------------|----|

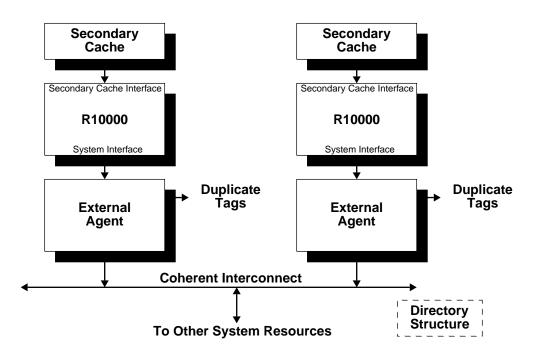

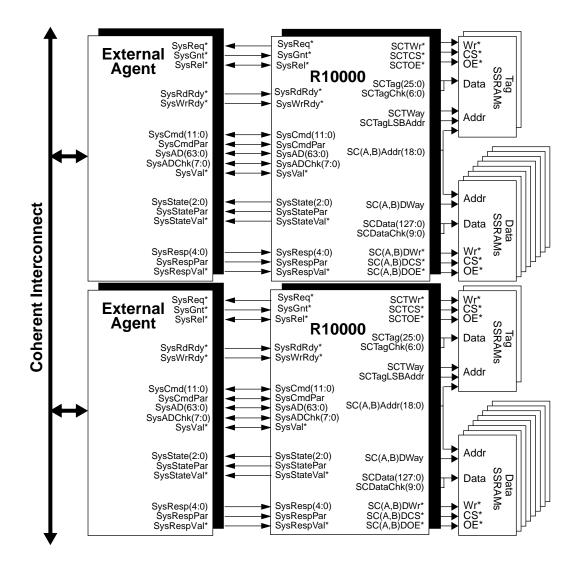

|     | Multiprocessor Systems                                 |    |

|     | Multiprocessor Systems Using Dedicated External Agents |    |

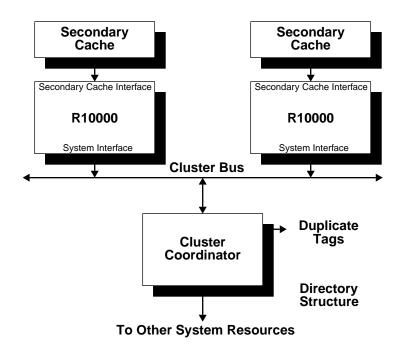

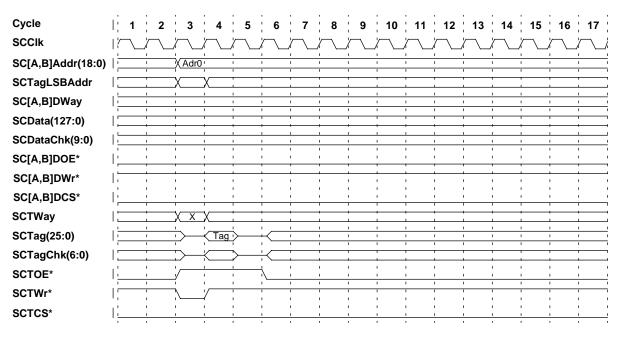

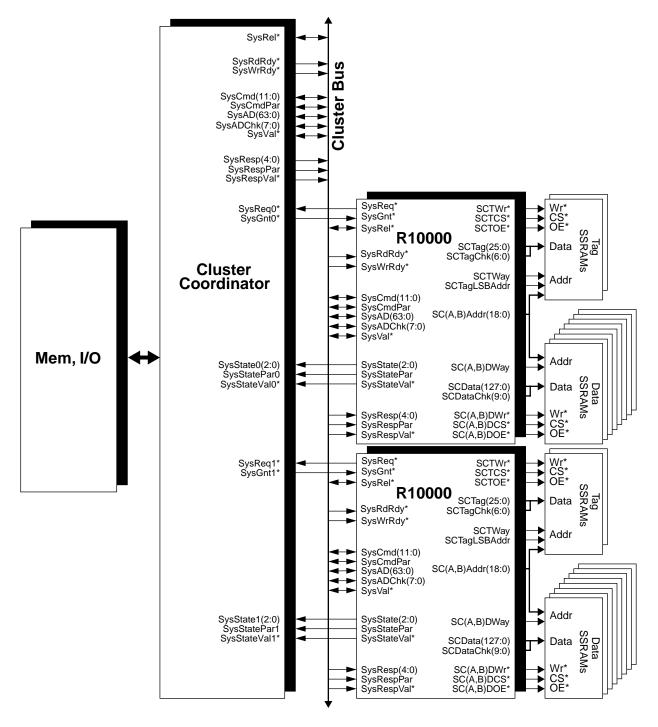

|     | Multiprocessor Systems Using a Cluster Bus             | 56 |

|     | · · · · · · · · · · · · · · · · · · ·                  |    |

## 3. Interface Signal Descriptions

| 3.1 | Power Interface Signals           | 58 |

|-----|-----------------------------------|----|

|     | Secondary Cache Interface Signals |    |

|     | System Interface Signals          |    |

|     | Test Interface Signals            |    |

|     | Unused Inputs                     |    |

## 4. Cache Organization and Coherency

| 4.1 | Primary Instruction Cache                           |    |

|-----|-----------------------------------------------------|----|

| 4.2 | Primary Instruction Cache<br>Primary Data Cache     |    |

|     | DCache set locking relaxed (R12000)                 |    |

| 4.3 | Secondary Cache                                     |    |

|     | <r12000></r12000>                                   |    |

| 4.4 | Cache Algorithms                                    | 74 |

|     | Descriptions of the Cache Algorithms                |    |

|     | Uncached                                            |    |

|     | Cacheable Noncoherent                               |    |

|     | Cacheable Coherent Exclusive                        |    |

|     | Cacheable Coherent Exclusive on Write               |    |

|     | Uncached Accelerated                                |    |

| 4.5 | Relationship Between Cached and Uncached Operations |    |

| 4.6 | Cache Algorithms and Processor Requests             |    |

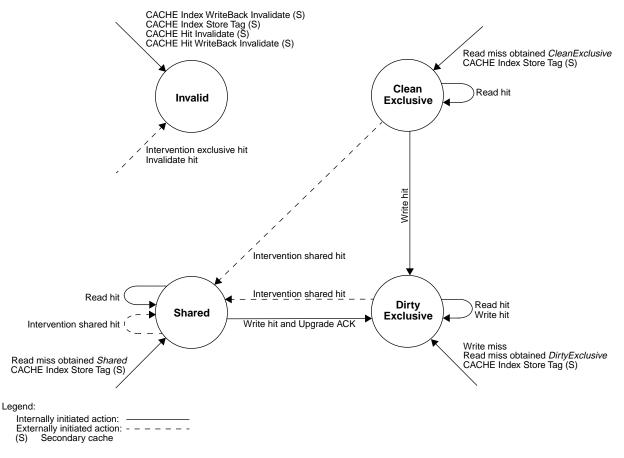

| 4.7 | Cache Block Ownership                               |    |

|     | •                                                   |    |

# 5. Secondary Cache Interface

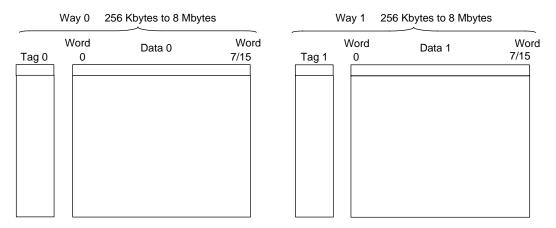

| 5.1 | Tag and Data Arrays                                                      |    |

|-----|--------------------------------------------------------------------------|----|

| 5.2 | Secondary Cache Interface Frequencies                                    |    |

| 5.3 | Secondary Cache Indexing                                                 | 84 |

|     | Indexing the Data Array                                                  | 84 |

|     | Indexing the Tag Array                                                   | 85 |

| 5.4 | Secondary Cache Way Prediction Table                                     | 86 |

|     | Increased the Way Prediction Table (MRU table) to 16K single-bit entries |    |

|     | Direct Cache Test Mode                                                   |    |

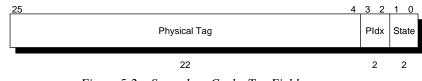

| 5.5 | Secondary Cache Tag                                                      |    |

|     | SCTag(25:4), Physical Tag                                                |    |

|     | SCTag(3:2), PIdx                                                         |    |

|     | SCTag(1:0), Cache Block State |  |

|-----|-------------------------------|--|

| 5.6 | Read Sequences                |  |

|     | 4-Word Read Sequence          |  |

|     | 8-Word Read Sequence          |  |

|     | 16 or 32-Word Read Sequence   |  |

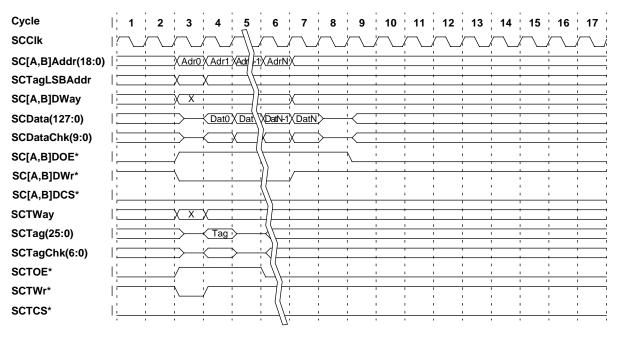

|     | Tag Read Sequence             |  |

| 5.7 | Write Sequences               |  |

|     | 4-Word Write Sequence         |  |

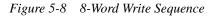

|     | 8-Word Write Sequence         |  |

|     | 16 or 32-Word Write Sequence  |  |

|     | Tag Write Sequence            |  |

|     |                               |  |

# 6. System Interface Operations

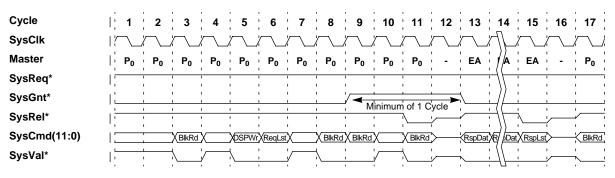

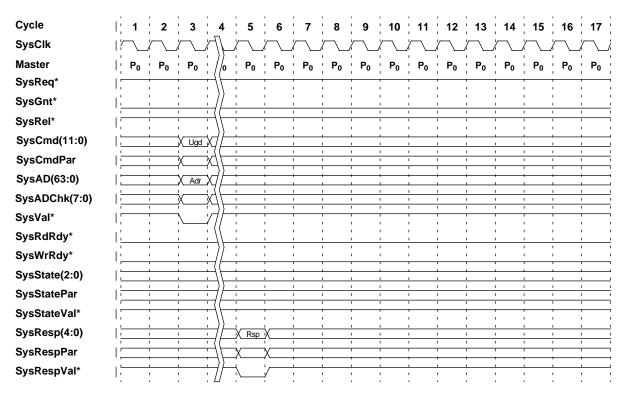

| 6.1  | Request and Response Cycles                           |     |

|------|-------------------------------------------------------|-----|

| 6.2  | System Interface Frequencies                          |     |

| 6.3  | Register-to-Register Operation                        |     |

| 6.4  | System Interface Signals                              |     |

| 6.5  | Master and Slave States                               |     |

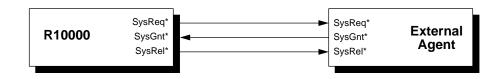

| 6.6  | Connecting to an External Agent                       |     |

| 6.7  | Cluster Bus                                           |     |

| 6.8  | System Interface Connections                          |     |

|      | Uniprocessor System                                   |     |

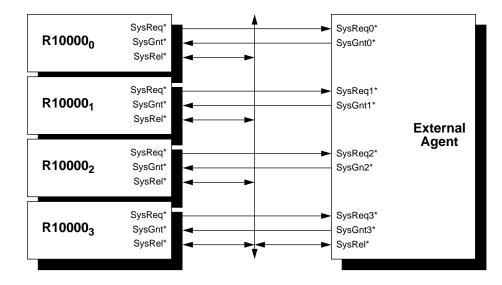

|      | Multiprocessor System Using Dedicated External Agents |     |

|      | Multiprocessor System Using the Cluster Bus           |     |

| 6.9  | System Interface Requests and Responses               |     |

|      | Processor Requests                                    |     |

|      | External Responses                                    |     |

|      | External Requests                                     |     |

|      | Processor Responses                                   |     |

|      | Outstanding Requests and Request Numbers              |     |

|      | Request and Response Relationship                     |     |

| 6.10 | System Interface Buffers                              |     |

|      | Cluster Request Buffer                                |     |

|      | Cached Request Buffer                                 |     |

|      | Incoming Buffer                                       |     |

|      | Outgoing Buffer                                       |     |

|      | Uncached Buffer                                       |     |

| 6.11 | System Interface Flow Control                         |     |

|      | Processor Write and Eliminate Request Flow Control    |     |

|      | Processor Read and Upgrade Request Flow Control       |     |

|      | Processor Coherency Data Response Flow Control        |     |

|      | External Request Flow Control                         |     |

|      | External Data Response Flow Control                   |     |

| 6.12 | System Interface Block Data Ordering                  |     |

|      | External Block Data Responses                         |     |

|      | Processor Coherency Data Responses                    | 116 |

|      | Processor Block Write Requests                        |     |

| 6.13 | System Interface Bus Encoding                         |     |

|      | SysCmd[11:0] Encoding                                 |     |

|      | SysCmd[11] Encoding                                   |     |

|      | SysCmd[10:0] Address Cycle Encoding                   |     |

|      | SysCmd[10:0] Data Cycle Encoding                      |     |

|      |                                                       |     |

|      | SysCmd[11:0] Map                                            |  |

|------|-------------------------------------------------------------|--|

|      | SysAD[63:0] Encoding                                        |  |

|      | SysAD[63:0] Address Cycle Encoding                          |  |

|      | SysAD[63:0] Data Cycle Encoding                             |  |

|      | SysState[2:0] Encoding                                      |  |

|      | SysResp[4:0] Encoding                                       |  |

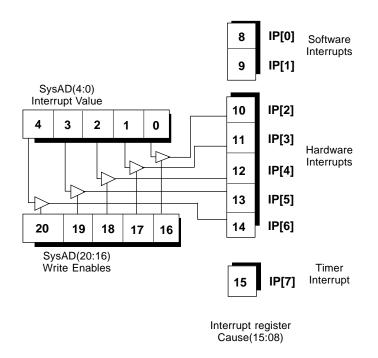

| 6.14 | Interrupts                                                  |  |

|      | Hardware Interrupts                                         |  |

|      | Software Interrupts                                         |  |

|      | Timer Interrupt                                             |  |

|      | Nonmaskable Interrupt                                       |  |

| 6.15 | Protocol Abbreviations                                      |  |

| 6.16 | System Interface Arbitration                                |  |

|      | System Interface Arbitration Rules                          |  |

|      | Uniprocessor System                                         |  |

|      | Multiprocessor System Using Cluster Bus                     |  |

| 6.17 | System Interface Request and Response Protocol              |  |

|      | Processor Request Protocol                                  |  |

|      | Processor Block Read Request Protocol                       |  |

|      | Processor Double/Single/Partial-Word Read Request Protocol  |  |

|      | Processor Block Write Request Protocol                      |  |

|      | Processor Double/Single/Partial-Word Write Request Protocol |  |

|      | Processor Upgrade Request Protocol                          |  |

|      | Processor Eliminate Request Protocol                        |  |

|      | Processor Request Flow Control Protocol                     |  |

|      | External Response Protocol                                  |  |

|      | External Block Data Response Protocol                       |  |

|      | External Double/Single/Partial-Word Data Response Protocol  |  |

|      | External Completion Response Protocol                       |  |

|      | External Request Protocol                                   |  |

|      | External Intervention Request Protocol                      |  |

|      | External Allocate Request Number Request Protocol           |  |

|      | External Invalidate Request Protocol                        |  |

|      | External Interrupt Request Protocol                         |  |

|      | Processor Response Protocol                                 |  |

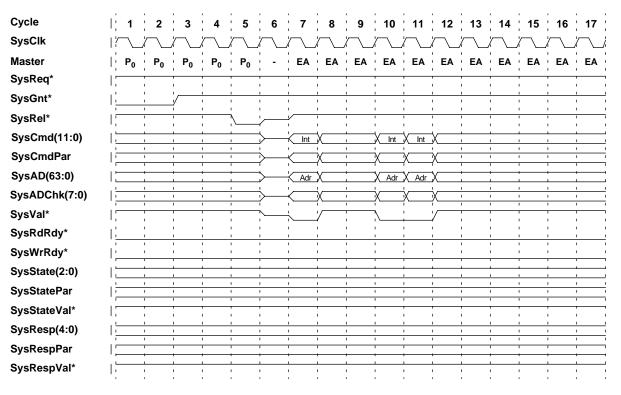

|      | Processor Coherency State Response Protocol                 |  |

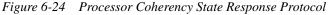

|      | Processor Coherency Data Response Protocol                  |  |

| 6.18 |                                                             |  |

|      | External Intervention Shared Request                        |  |

|      | External Intervention Exclusive Request                     |  |

|      | External Invalidate Request                                 |  |

|      | External Coherency Request Action                           |  |

|      | Coherency Conflicts                                         |  |

|      | Internal Coherency Conflicts                                |  |

|      | External Coherency Conflicts                                |  |

|      | External Coherency Request Latency                          |  |

|      | SysGblPerf* Signal                                          |  |

| 6.19 | Cluster Bus Operation                                       |  |

| 6.20 | Support for I/O                                             |  |

| 6.21 | Support for External Duplicate Tags                         |  |

| 6.22 | Support for a Directory-Based Coherency Protocol            |  |

| 6.23 | Support for Uncached Attribute                              |  |

| 6.24 | Support for Hardware Emulation                              |  |

# 7. Clock Signals

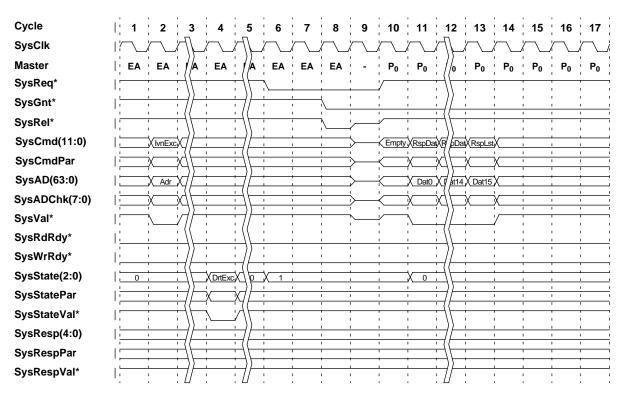

| 7.1 | System Interface Clock and Internal Processor Clock Domains | 178 |

|-----|-------------------------------------------------------------|-----|

|     | Secondary Cache Clock                                       |     |

|     | Phase-Locked-Loop                                           |     |

## 8. Initialization

| 8.1 | Initialization of Logical Registers | 182 |

|-----|-------------------------------------|-----|

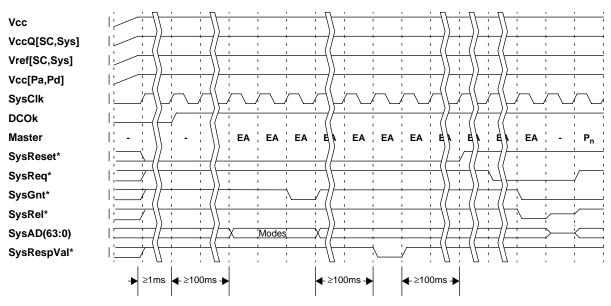

|     | Power-On Reset Sequence             |     |

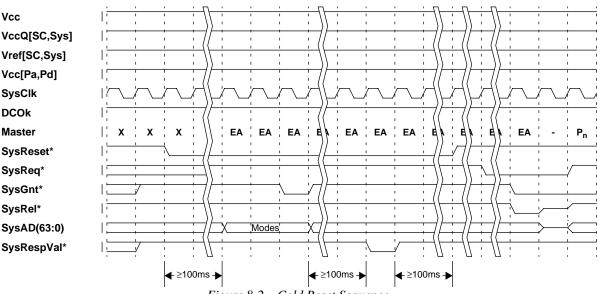

|     | Cold Reset Sequence                 |     |

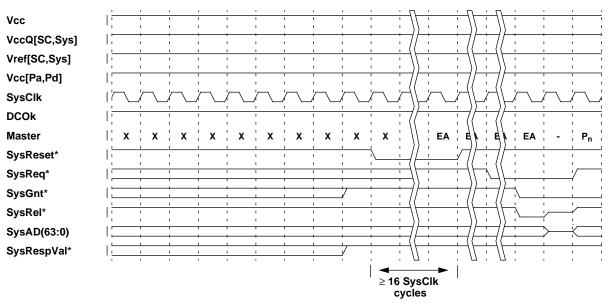

|     | Soft Reset Sequence                 |     |

| 8.5 | Mode Bits                           | 186 |

# 9. Error Protection and Handling

| 9.1  | Correctable Errors                                      |  |

|------|---------------------------------------------------------|--|

| 9.2  | Uncorrectable Errors                                    |  |

| 9.3  | Propagation of Uncorrectable Errors                     |  |

| 9.4  | Cache Error Exception                                   |  |

| 9.5  | CP0 CacheErr Register EW Bit                            |  |

| 9.6  | CP0 Status Register DE Bit                              |  |

| 9.7  | CACHE Instruction                                       |  |

| 9.8  | Error Protection Schemes Used by R10000                 |  |

|      | Parity                                                  |  |

|      | Sparse Encoding                                         |  |

|      | ECC                                                     |  |

| 9.9  | Primary Instruction Cache Error Protection and Handling |  |

|      | Error Protection                                        |  |

|      | Error Handling                                          |  |

| 9.10 | Primary Data Cache Error Protection and Handling        |  |

|      | Error Protection                                        |  |

|      | Error Handling                                          |  |

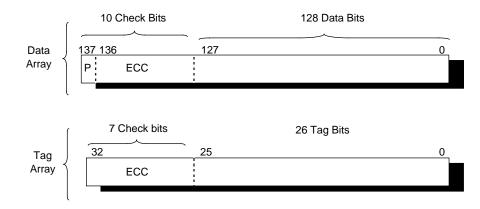

| 9.11 | Secondary Cache Error Protection and Handling           |  |

|      | Error Protection                                        |  |

|      | Error Handling                                          |  |

|      | Data Array                                              |  |

|      | Tag Array                                               |  |

| 9.12 | System Interface Error Protection and Handling          |  |

|      | Error Protection                                        |  |

|      | Error Handling                                          |  |

|      | SysCmd(11:0) Bus                                        |  |

|      | SysAD(63:0) Bus                                         |  |

|      | SysState(2:0) Bus                                       |  |

|      | SysResp(4:0) Bus                                        |  |

|      | Protocol Observation                                    |  |

# **10. JTAG Interface Operation**

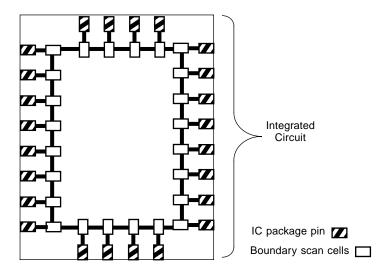

| 10.1 | Test Access Port (TAP) |  |

|------|------------------------|--|

|      | TAP Controller (Input) |  |

| 10.2 | Instruction Register   |  |

| 10.3 | Bypass Register        |      |

|------|------------------------|------|

| 10.4 | Boundary Scan Register | .214 |

# **11. Electrical Specifications**

| 11.1 | DC Electrical Specification                 |  |

|------|---------------------------------------------|--|

|      | DC Power Supply Levels                      |  |

|      | DCOk and Power Supply Sequencing            |  |

|      | Maximum Operating Conditions                |  |

|      | Input Signal Level Sensing                  |  |

|      | Mode Definitions                            |  |

|      | Vref[SC,Sys]                                |  |

|      | DC Input/Output Specifications              |  |

| 11.2 | AC Electrical Specification                 |  |

|      | Maximum Operating Conditions                |  |

|      | Test Specification                          |  |

|      | Secondary Cache and System Interface Timing |  |

|      | Enable/Output Delay, Setup, Hold Time       |  |

|      | Asynchronous Inputs                         |  |

| 11.3 | Signal Integrity Issues                     |  |

|      | Reference Voltage                           |  |

|      | Power Supply Regulation                     |  |

|      | Maximum Input Voltage Levels                |  |

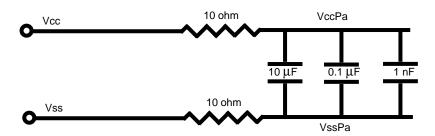

|      | Decoupling Capacitance                      |  |

|      |                                             |  |

# 12. Packaging

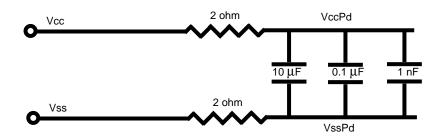

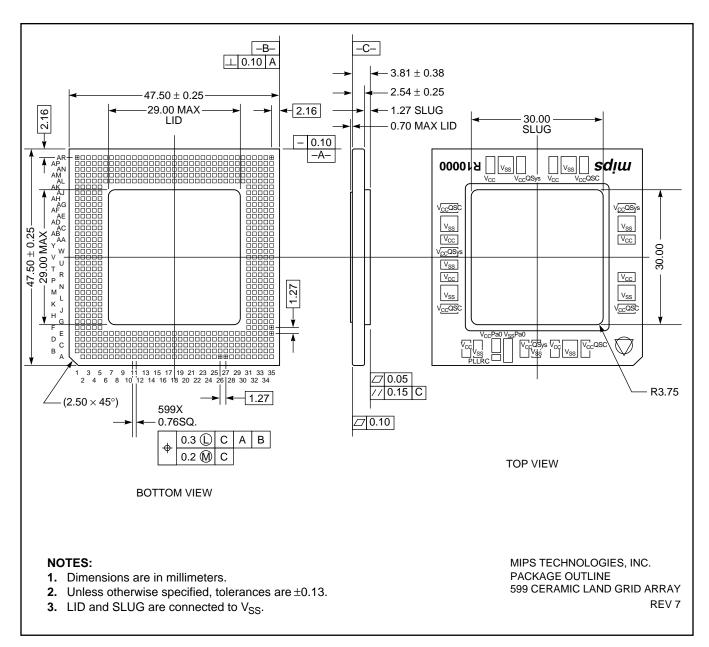

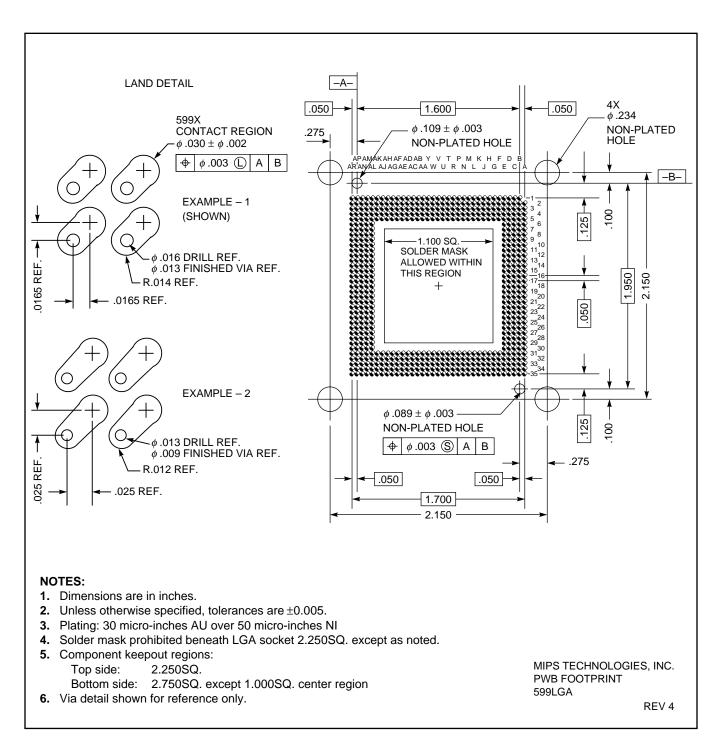

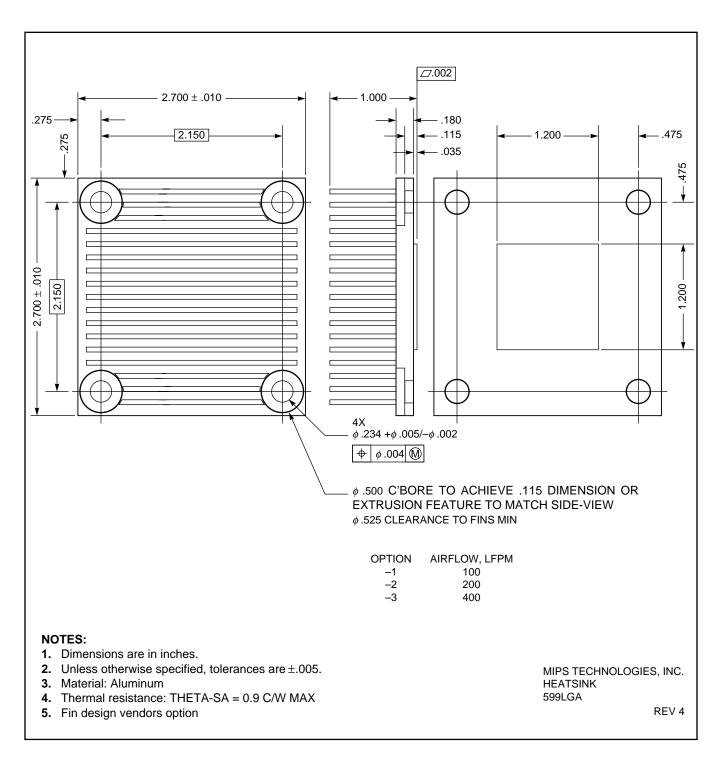

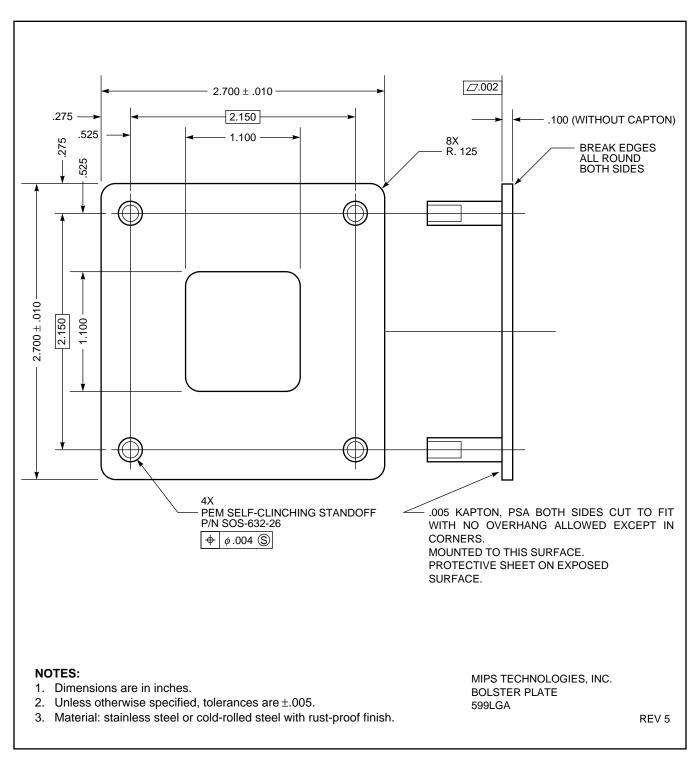

| 12.1 | R10000 Single-Chip Package, 599CLGA |  |

|------|-------------------------------------|--|

|      | Mechanical Characteristics          |  |

|      | Electrical Characteristics          |  |

|      | Thermal Characteristics             |  |

|      | Assembly Drawings and Pinout List   |  |

|      | 599CLGA Pinout                      |  |

# 13. Coprocessor 0

| 13.1  | Index Register (0)                                 | 243 |

|-------|----------------------------------------------------|-----|

| 13.2  | Index Register (0)<br>Random Register (1)          | 244 |

| 13.3  | EntryLo0 (2), and EntryLo1 (3) Registers           | 245 |

| 13.4  | Context (4)                                        | 247 |

| 13.5  | PageMask Register (5)                              | 248 |

| 13.6  | Wired Register (6)                                 | 249 |

| 13.7  | BadVAddr Register (8)                              |     |

| 13.8  | Count and Compare Registers (9 and 11)             | 250 |

| 13.9  | EntryHi Register (10)                              | 251 |

| 13.10 | Status Register (12)                               | 252 |

|       | Status Register Fields                             | 254 |

|       | Diagnostic Status Field                            | 255 |

|       | Coprocessor Accessibility                          | 257 |

| 13.11 | Cause Register (13)                                | 258 |

| 13.12 | Exception Program Counter (14)                     |     |

| 13.13 | Processor Revision Identifier (PRId) Register (15) | 261 |

| 13.14 | Config Register (16)                                          |     |

|-------|---------------------------------------------------------------|-----|

| 13.15 | Load Linked Address (LLAddr) Register (17)                    |     |

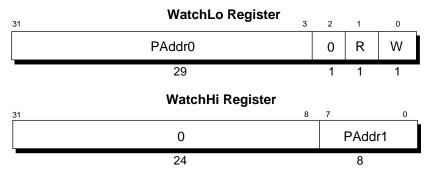

| 13.16 | WatchLo (18) and WatchHi (19) Registers                       |     |

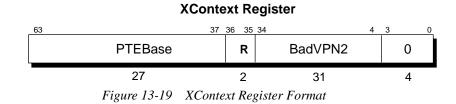

| 13.17 | XContext Register (20)                                        |     |

| 13.18 | FrameMask Register (21)                                       |     |

| 13.19 | Diagnostic Register (22)                                      |     |

| 13.20 | Performance Counter Registers (25)                            | 270 |

| 13.21 | ECC Register (26)                                             | 279 |

| 13.22 | CacheErr Register (27)                                        |     |

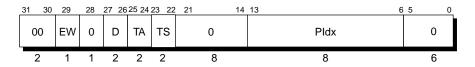

|       | CacheErr Register Format for Primary Instruction Cache Errors |     |

|       | CacheErr Register Format for Primary Data Cache Errors        |     |

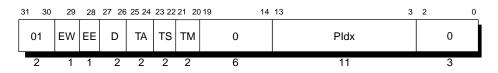

|       | CacheErr Register Format for Secondary Cache Errors           |     |

|       | CacheErr Register Format for System Interface Errors          |     |

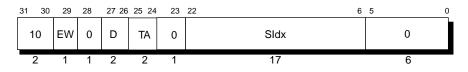

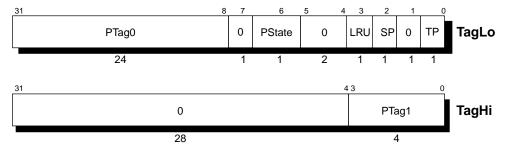

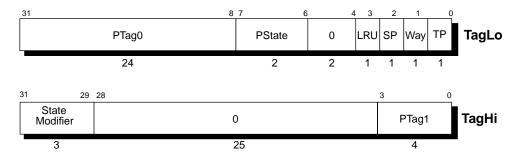

| 13.23 | TagLo (28) and TagHi (29) Registers                           |     |

|       | CacheOp is Index Load/Store Tag                               |     |

|       | Primary Instruction Cache Operation                           |     |

|       | Primary Data Cache Operation                                  |     |

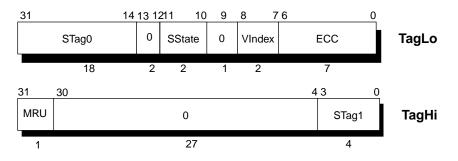

|       | Secondary Cache Operation                                     |     |

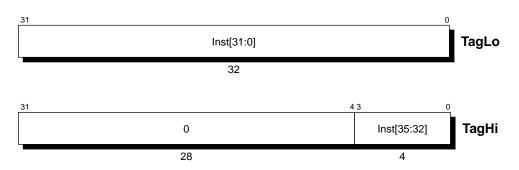

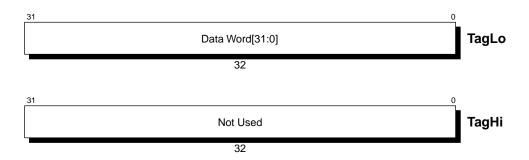

|       | CacheOp is Index Load/Store Data                              |     |

|       | Primary Instruction Cache Operation                           |     |

|       |                                                               |     |

|       | Secondary Cache Operation                                     |     |

| 13.24 | ErrorEPC Register (30)                                        |     |

| 13.24 |                                                               |     |

# 14. Floating-Point Unit

| 14.1 | Floating Point Unit Operations                      |  |

|------|-----------------------------------------------------|--|

| 14.2 | Floating-Point Unit Control                         |  |

|      | Eliminate traps for Denorm/NaN FP inputs (R12000)   |  |

| 14.3 | Floating-Point General Registers (FGRs)             |  |

|      | 32- and 64-Bit Operations                           |  |

|      | Load and Store Operations                           |  |

| 14.4 | Floating-Point Control Registers                    |  |

|      | Floating-Point Implementation and Revision Register |  |

|      | Floating-Point Status Register (FSR)                |  |

|      | Bit Descriptions of the FSR                         |  |

|      | Loading the FSR                                     |  |

|      |                                                     |  |

# **15. Memory Management**

| 15.1 | Processor Modes                                           |  |

|------|-----------------------------------------------------------|--|

|      | Processor Operating Modes                                 |  |

|      | Addressing Modes                                          |  |

| 15.2 | Virtual Address Space                                     |  |

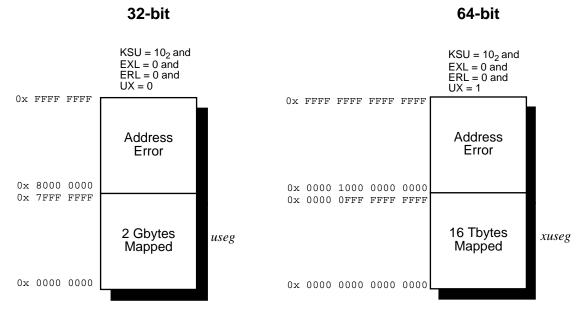

|      | User Mode Operations                                      |  |

|      | 32-bit User Mode (useg)                                   |  |

|      | 64-bit User Mode (xuseg)                                  |  |

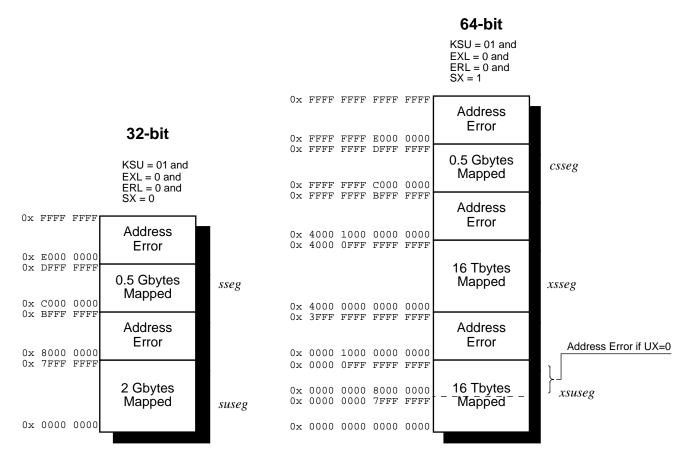

|      | Supervisor Mode Operations                                |  |

|      | 32-bit Supervisor Mode, User Space (suseg)                |  |

|      | 32-bit Supervisor Mode, Supervisor Space (sseg)           |  |

|      | 64-bit Supervisor Mode, User Space (xsuseg)               |  |

|      | 64-bit Supervisor Mode, Current Supervisor Space (xsseg)  |  |

|      | 64-bit Supervisor Mode, Separate Supervisor Space (csseg) |  |

|      |                                                           |  |

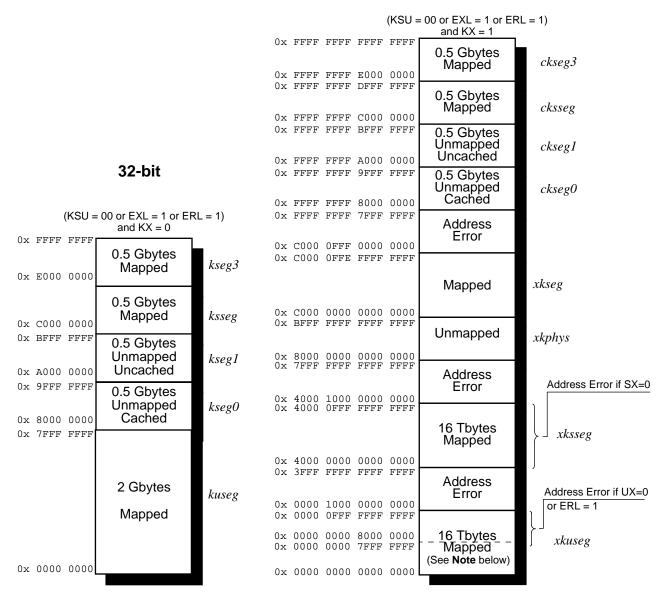

|      | Kernel Mode Operations                                                  |  |

|------|-------------------------------------------------------------------------|--|

|      | 32-bit Kernel Mode, User Space (kuseg)                                  |  |

|      | 32-bit Kernel Mode, Kernel Space 0 (kseg0)                              |  |

|      | 32-bit Kernel Mode, Kernel Space 1 (kseg1)                              |  |

|      | 32-bit Kernel Mode, Supervisor Space (ksseg)                            |  |

|      | 32-bit Kernel Mode, Kernel Space 3 (kseg3)                              |  |

|      | 64-bit Kernel Mode, User Space (xkuseg)                                 |  |

|      | 64-bit Kernel Mode, Current Supervisor Space (xksseg)                   |  |

|      | 64-bit Kernel Mode, Physical Spaces (xkphys)                            |  |

|      | 64-bit Kernel Mode, Kernel Space (xkseg)                                |  |

|      | 64-bit Kernel Mode, Compatibility Spaces (ckseg1:0, cksseg, ckseg3)     |  |

|      | Address Space Access Privilege Differences Between the R4400 and R10000 |  |

| 15.3 | Virtual Address Translation                                             |  |

|      | Virtual Pages                                                           |  |

|      | Virtual Page Size Encodings                                             |  |

|      | Using the TLB                                                           |  |

|      | Cache Algorithm Field                                                   |  |

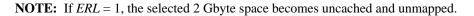

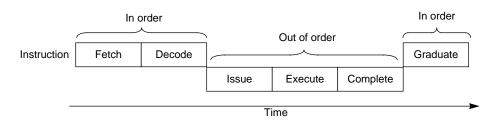

|      | Format of a TLB Entry                                                   |  |

|      | Address Translation                                                     |  |

|      | Address Space Identification (ASID)                                     |  |

|      | Global Processes (G)                                                    |  |

|      | Avoiding TLB Conflict                                                   |  |

# 16. CPU Exceptions

| 16.1 | Causing and Returning from an Exception |  |  |  |

|------|-----------------------------------------|--|--|--|

| 16.2 | Exception Vector Locations              |  |  |  |

| 16.3 | 3 TLB Refill Vector Selection           |  |  |  |

|      | Priority of Exceptions                  |  |  |  |

|      | Cold Reset Exception                    |  |  |  |

|      | Soft Reset Exception                    |  |  |  |

|      | NMI Exception                           |  |  |  |

|      | Address Error Exception                 |  |  |  |

|      | TLB Exceptions                          |  |  |  |

|      | TLB Refill Exception                    |  |  |  |

|      | TLB Invalid Exception                   |  |  |  |

|      | TLB Modified Exception                  |  |  |  |

|      | Cache Error Exception                   |  |  |  |

|      | Virtual Coherency Exception             |  |  |  |

|      | Bus Error Exception                     |  |  |  |

|      | Integer Overflow Exception              |  |  |  |

|      | Trap Exception                          |  |  |  |

|      | System Call Exception                   |  |  |  |

|      | Breakpoint Exception                    |  |  |  |

|      | Reserved Instruction Exception          |  |  |  |

|      | Coprocessor Unusable Exception          |  |  |  |

|      | Floating-Point Exception                |  |  |  |

|      | Watch Exception                         |  |  |  |

|      | Interrupt Exception                     |  |  |  |

| 16.4 | MIPSIV Instructions                     |  |  |  |

| 16.5 | COP0 Instructions                       |  |  |  |

| 16.6 | COP1 Instructions                       |  |  |  |

| 16.7 | COP2 Instructions                       |  |  |  |

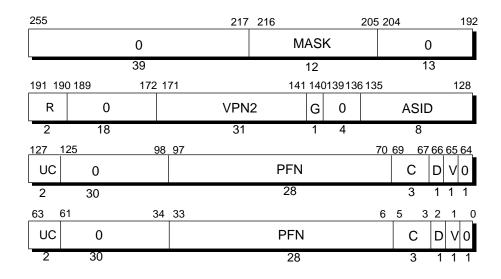

## 17. Cache Test Mode

| 17.1 | Interface Signals              |  |

|------|--------------------------------|--|

| 17.2 | System Interface Clock Divisor |  |

| 17.3 | Entering Cache Test Mode       |  |

|      | Exit Sequence                  |  |

|      | SysAD(63:0) Encoding           |  |

|      | Cache Test Mode Protocol       |  |

|      | Normal Write Protocol          |  |

|      | Auto-Increment Write Protocol  |  |

|      | Normal Read Protocol           |  |

|      | Auto-Increment Read Protocol   |  |

|      |                                |  |

# Appendix A Glossary

| A.1  | Superscalar Processor                                                   | 358 |

|------|-------------------------------------------------------------------------|-----|

| A.2  | Superscalar Processor<br>Pipeline                                       | 358 |

| A.3  | Pipeline Latency                                                        |     |

| A.4  | Pipeline Repeat Rate                                                    | 358 |

| A.5  | Out-of-Order Execution                                                  | 358 |

| A.6  | Dynamic Scheduling                                                      | 359 |

| A.7  | Instruction Fetch, Decode, Issue, Execution, Completion, and Graduation |     |

| A.8  | Active List                                                             | 359 |

| A.9  | Free List and Busy Registers                                            |     |

| A.10 | Register Renaming                                                       |     |

| A.11 | Nonblocking Loads and Stores                                            |     |

| A.12 | Speculative Branching                                                   |     |

| A.13 | Logical and Physical Registers                                          |     |

| A.14 | Register Files                                                          |     |

| A.15 | ANDES Architecture                                                      |     |

|      |                                                                         |     |

# Appendix B Differences between R10000 and R12000

| B.1  | Mode bits changed in R12000                                              |  |

|------|--------------------------------------------------------------------------|--|

| B.2  | DSD (Delay Speculative Dirty)                                            |  |

| B.3  | Config Register[22]                                                      |  |

| B.4  | Config Register[23]                                                      |  |

| B.5  | Changes in the Branch Diag Register                                      |  |

| B.6  | Eliminate traps for Denorm/NaN FP inputs                                 |  |

| B.7  | Increase in pre-decode buffering                                         |  |

| B.8  | Increased penalty for indirect branches                                  |  |

| B.9  | Addition of a Branch Target Address Cache                                |  |

| B.10 | Use of global history in branch-prediction                               |  |

| B.11 | Increase in branch prediction table size                                 |  |

| B.12 | Address calculation for load/store instructions uses integer queue       |  |

| B.13 | Load/store dependency is speculatively ignored                           |  |

| B.14 | DCache set locking relaxed                                               |  |

| B.15 | SC refill blocking reduced                                               |  |

| B.16 | Increased the Way Prediction Table (MRU table) to 16K single-bit entries |  |

| B.17 | Additional cycles for System Interface transactions                      |  |

| B.18 | FP and Integer-Queue Issue Policy                                        |  |

| B.19 | Active List entries are increased to 48                                  |  |

|      |                                                                          |  |

| B.20 | Cache Error inhibits graduation                                | 373 |

|------|----------------------------------------------------------------|-----|

|      | Changed Spare(1, 3) pins to NC (No Connection)                 |     |

| B.22 | CacheOp Index Write Back Invalidate(D) also clears Primary Tag | 373 |

| B.23 | Summary of the differences                                     | 374 |

# Appendix C Index

# 1. Introduction to the R10000 Processor

This user's manual describes the R10000 superscalar microprocessor for the system designer, paying special attention to the external interface and the transfer protocols.

This chapter describes the following:

- MIPS<sup>TM</sup> ISA

- what makes a generic superscalar microprocessor

- specifics of the R10000 superscalar microprocessor

- implementation-specific CPU instructions

## 1.1 MIPS Instruction Set Architecture (ISA)

MIPS has defined an instruction set architecture (ISA), implemented in the following sets of CPU designs:

- MIPS I, implemented in the  $R2000^{TM}$  and R3000

- MIPS II, implemented in the R6000<sup>TM</sup>

- MIPS III, implemented in the R4400

- MIPS IV, implemented in the  $R8000^{TM}$  and R10000

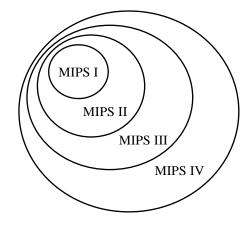

The original MIPS I CPU ISA has been extended forward three times, as shown in Figure 1-1; each extension is backward compatible. The ISA extensions are inclusive; each new architecture level (or version) includes the former levels.<sup>†</sup>

Figure 1-1 MIPS ISA with Extensions

The practical result is that a processor implementing MIPS IV is also able to run MIPS I, MIPS II, or MIPS III binary programs without change.

<sup>&</sup>lt;sup>†</sup> For more ISA information, please refer to the *MIPS IV Instruction Set Architecture*, published by MIPS Technologies, and written by Charles Price. Contact information is provided both in the *Preface*, and inside the front cover, of this manual.

## 1.2 What is a Superscalar Processor?

A superscalar processor is one that can fetch, execute and complete more than one instruction in parallel.

#### **Pipeline and Superpipeline Architecture**

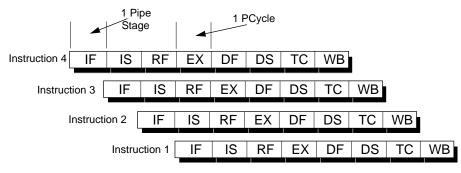

Previous MIPS processors had linear pipeline architectures; an example of such a linear pipeline is the R4400 superpipeline, shown in Figure 1-2. In the R4400 superpipeline architecture, an instruction is executed each cycle of the pipeline clock (PCycle), or each *pipe stage*.

Figure 1-2 R4400 Pipeline

#### Superscalar Architecture

The structure of 4-way superscalar pipeline is shown in Figure 1-3. At each stage, four instructions are handled in parallel. Note that there is only one EX stage for integers.

| Instruction 1 | IF            | ID | IS | EX | WB | IF = instruction fetch                            |

|---------------|---------------|----|----|----|----|---------------------------------------------------|

| Instruction 2 | IF            | ID | IS | EX | WB | ID = instruction decode and dependency            |

| Instruction 3 | IF            | ID | IS | EX | WB | IS = instruction issue<br>EX = execution (1 only) |

| Instruction 4 | IF            | ID | IS | EX | WB | WB = write back                                   |

|               | Instruction 5 | IF | ID | IS | EX | WB                                                |

|               | Instruction 6 | IF | ID | IS | EX | WB                                                |

|               | Instruction 7 | IF | ID | IS | EX | WB                                                |

|               | Instruction 8 | IF | ID | IS | EX | WB                                                |

Figure 1-3 4-Way Superscalar Pipeline

## 1.3 What is an R10000 Microprocessor?

The R10000 processor is a single-chip superscalar RISC microprocessor that is a followon to the MIPS RISC processor family that includes, chronologically, the R2000, R3000, R6000, R4400, and R8000.

The R10000 processor uses the MIPS ANDES architecture, or *Architecture with Non*sequential Dynamic Execution Scheduling.

The R10000 processor has the following major features (terms in **bold** are defined in the Glossary):

- it implements the 64-bit MIPS IV instruction set architecture (ISA)

- it can decode four instructions each pipeline cycle, appending them to one of three *instruction queues*

- it has five *execution pipelines* connected to separate internal integer and floating-point execution (or *functional*) units

- it uses dynamic instruction scheduling and out-of-order execution

- it uses speculative instruction issue (also termed "speculative branching")

- it uses a precise exception model (exceptions can be traced back to the instruction that caused them)

- it uses non-blocking caches

- it has separate on-chip 32-Kbyte primary instruction and data caches

- it has individually-optimized secondary cache and System interface ports

- it has an internal controller for the external secondary cache

- it has an internal System interface controller with multiprocessor support

### Errata

The R10000 processor is implemented using 0.35-micron CMOS VLSI circuitry on a single 17 mm-by-18 mm chip that contains about <u>6.7</u> million transistors, including about 4.4 million transistors in its primary caches.

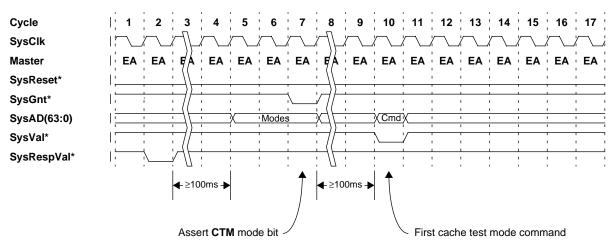

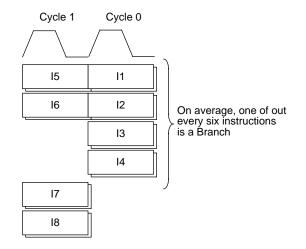

#### **R10000 Superscalar Pipeline**

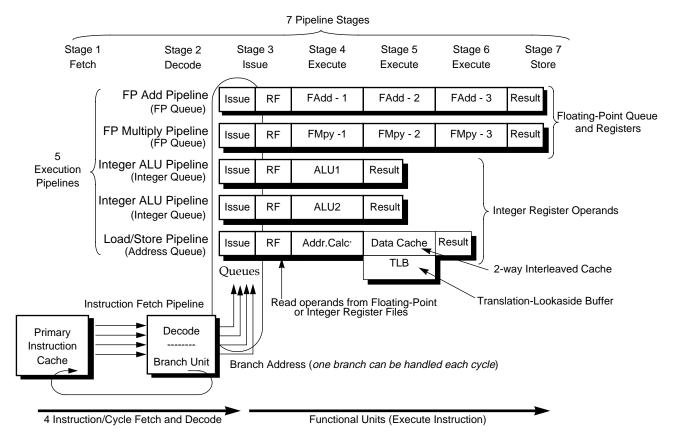

The R10000 superscalar processor fetches and decodes four instructions in parallel each cycle (or pipeline stage). Each pipeline includes stages for fetching (stage 1 in Figure 1-4), decoding (stage 2) issuing instructions (stage 3), reading register operands (stage 3), executing instructions (stages 4 through 6), and storing results (stage 7).

Figure 1-4 Superscalar Pipeline Architecture in the R10000

#### **Instruction Queues**

As shown in Figure 1-4, each instruction decoded in stage 2 is appended to one of three instruction *queues*:

- integer queue

- address queue

- floating-point queue

#### **Execution Pipelines**

The three instruction queues can issue (see the Glossary for a definition of *issue*) one new instruction per cycle to each of the five execution pipelines:

- the integer queue issues instructions to the two integer ALU pipelines

- the address queue issues one instruction to the Load/Store Unit pipeline

- the floating-point queue issues instructions to the floating-point adder and multiplier pipelines

A sixth pipeline, the fetch pipeline, reads and decodes instructions from the instruction cache.

#### Load/store dependency is speculatively ignored (R12000)

When a load follows a store in program-order, and the address of the load is known to the Address Queue (AQ) before the address of the store, then the AQ may speculatively issue the load to tag-check and data access. When the address of the store is determined, the AQ can undo the effects of the load through the use of the "soft-exception" mechanism. Since almost all loads which are actually dependent on previous stores use the same registers to form their addresses, normally either the two instructions are independent, or their addresses are resolved in program order, so the soft-exception should occur rarely.

#### 64-bit Integer ALU Pipeline

The 64-bit integer pipeline has the following characteristics:

- it has a 16-entry integer instruction queue that dynamically issues instructions

- it has a 64-bit 64-location integer physical register file, with seven read and three write ports (32 logical registers; see *register renaming* in the Glossary)

- it has two 64-bit arithmetic logic units:

- ALU1 contains an arithmetic-logic unit, shifter, and integer branch comparator

- ALU2 contains an arithmetic-logic unit, integer multiplier, and divider

#### **Load/Store Pipeline**

The load/store pipeline has the following characteristics:

- it has a 16-entry address queue that dynamically issues instructions, and uses the integer register file for base and index registers

- it has a 16-entry address stack for use by non-blocking loads and stores

- it has a 44-bit virtual address calculation unit

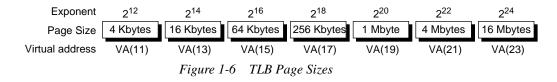

- it has a 64-entry fully associative **Translation-Lookaside Buffer** (TLB), which converts virtual addresses to physical addresses, using a 40-bit physical address. Each entry maps two pages, with sizes ranging from 4 Kbytes to 16 Mbytes, in powers of 4.

#### **64-bit Floating-Point Pipeline**

The 64-bit floating-point pipeline has the following characteristics:

- it has a 16-entry instruction queue, with dynamic issue

- it has a 64-bit 64-location floating-point physical register file, with five read and three write ports (32 logical registers)

- it has a 64-bit parallel multiply unit (3-cycle pipeline with 2-cycle latency) which also performs move instructions

- it has a 64-bit add unit (3-cycle pipeline with 2-cycle latency) which handles addition, subtraction, and miscellaneous floating-point operations

- it has separate 64-bit divide and square-root units which can operate concurrently (these units share their issue and completion logic with the floating-point multiplier)

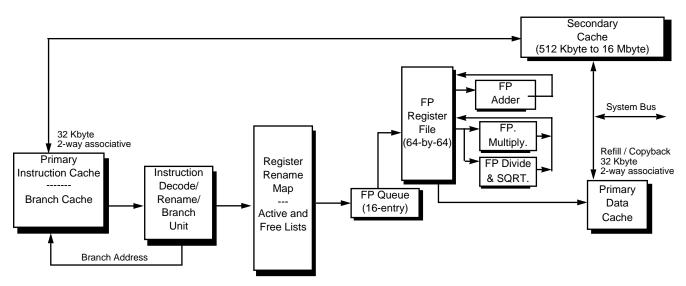

A block diagram of the processor and its interfaces is shown in Figure 1-5, followed by a description of its major logical blocks.

Figure 1-5 Block Diagram of the R10000 Processor

## **Functional Units**

★

The five execution pipelines allow overlapped instruction execution by issuing instructions to the following five functional units:

- two integer ALUs (ALU1 and ALU2)

- the Load/Store unit (address calculate)

- the floating-point adder

- the floating-point multiplier

There are also three "iterative" units to compute more complex results:

- Integer multiply and divide operations are performed by an Integer Multiply/ Divide execution unit; these instructions are issued to ALU2. ALU2 remains busy for the duration of the divide.

- Floating-point divides are performed by the Divide execution unit; these instructions are issued to the floating-point multiplier.

- Floating-point square root are performed by the Square-root execution unit; these instructions are issued to the floating-point multiplier.

#### Increase in pre-decode buffering (R12000)

Up to 12 instruction may be buffered before being decoded. This should normally be invisible to the end user, but can be important when debugging systems in uncached-mode, since fetch and decode are now further de-coupled.

#### **Primary Instruction Cache (I-cache)**

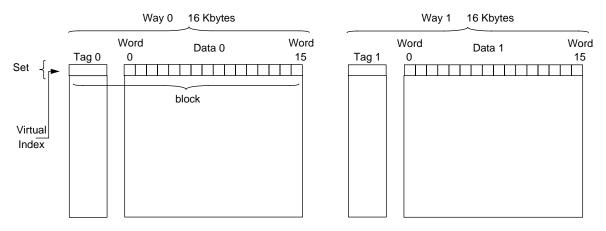

The primary instruction cache has the following characteristics:

- it contains 32 Kbytes, organized into 16-word blocks, is 2-way set associative, using a **least-recently used** (LRU) replacement algorithm

- it reads four consecutive instructions per cycle, beginning on any word boundary within a cache block, but cannot fetch across a block boundary.

- its instructions are predecoded, its fields are rearranged, and a 4-bit unit select code is appended

- it checks parity on each word

- it permits non-blocking instruction fetch

#### **Primary Data Cache (D-cache)**

The primary data cache has the following characteristics:

- it has two interleaved arrays (two 16 Kbyte ways)

- it contains 32 Kbytes, organized into 8-word blocks, is 2-way set associative, using an LRU replacement algorithm.

- it handles 64-bit load/store operations

- it handles 128-bit refill or write-back operations

- it permits non-blocking loads and stores

- it checks parity on each byte

#### ★ Branch Target Address Cache (R12000)

This 32-entry two-way set-associative cache holds the target addresses of previously-taken branches. When a branch is executed a hit in the BTAC eliminates the one-cycle fetch bubble with the R10000 experiences for every taken branch. However, if a branch which hits in the BTAC is actually predicted not-taken, then a one cycle fetch bubble is introduced where none was present before. Performance simulations indicate that the BTAC is a net win, but because of its "mixed-blessing" nature, a mechanism has been provided to disable it via software. (See description of changes to diag register).

#### **Instruction Decode And Rename Unit**

The instruction decode and rename unit has the following characteristics:

- it processes 4 instructions in parallel

- it replaces logical register numbers with physical register numbers (register renaming)

- it maps integer registers into a 33-word-by-6-bit mapping table that has 4 write and 12 read ports

- it maps floating-point registers into a 32-word-by-6-bit mapping table that has 4 write and 16 read ports

- it has a 32-entry active list of all instructions within the pipeline.

**Branch Unit**

The branch unit has the following characteristics:

- it allows one branch per cycle

- conditional branches can be executed speculatively, up to 4-deep

- it has a 44-bit adder to compute branch addresses

- it has a 4-quadword branch-resume buffer, used for reversing mispredicted speculatively-taken branches

Errata

- the Branch <u>Return Cache</u> contains four instructions following a subroutine call, for rapid use when returning from leaf subroutines

- it has program trace RAM that stores the program counter for each instruction in the pipeline

## **External Interfaces**

$\star$

The external interfaces have the following characteristics:

- a 64-bit System interface allows direct-connection for 2-way to 4-way multiprocessor systems. 8-bit ECC Error Check and Correction is made on address and data transfers.

- a secondary cache interface with 128-bit data path and tag fields. 9-bit ECC Error Check and Correction is made on data quadwords, 7-bit ECC is made on tag words. It allows connection to an external secondary cache that can range from 512 Kbytes to 16 Mbytes, using external static RAMs. The secondary cache can be organized into either 16- or 32-word blocks, and is 2-way set associative.

Bit definitions are given in Chapter 3.

#### Additional cycles for System Interface transactions (R12000)

All transactions which go through the system interface unit (in particular, SCache refills and writebacks) have one additional CPU-clock of latency added to them.

## **1.4 Instruction Queues**

The processor keeps decoded instructions in three instruction queues, which dynamically issue instructions to the execution units. The queues allow the processor to fetch instructions at its maximum rate, without stalling because of instruction conflicts or dependencies.

Each queue uses instruction tags to keep track of the instruction in each execution pipeline stage. These tags set a *Done* bit in the active list as each instruction is completed.

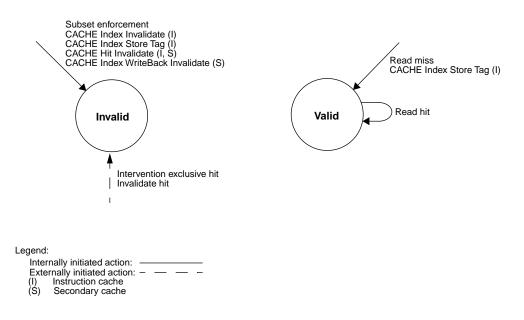

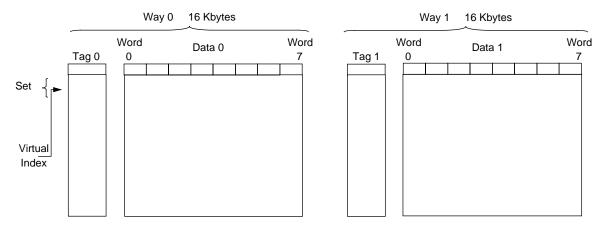

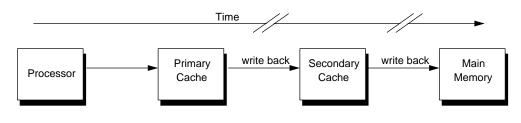

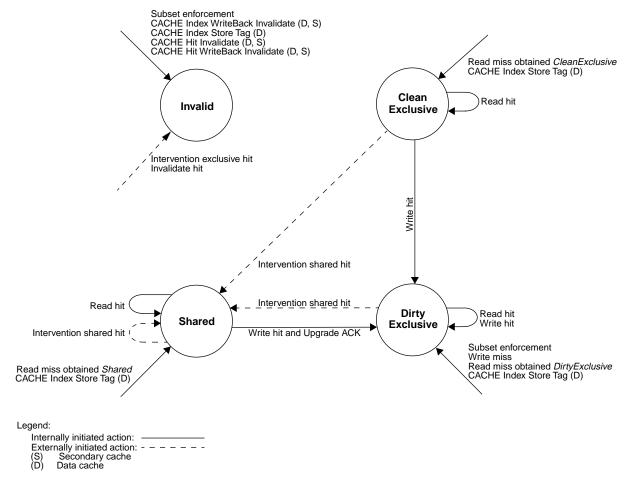

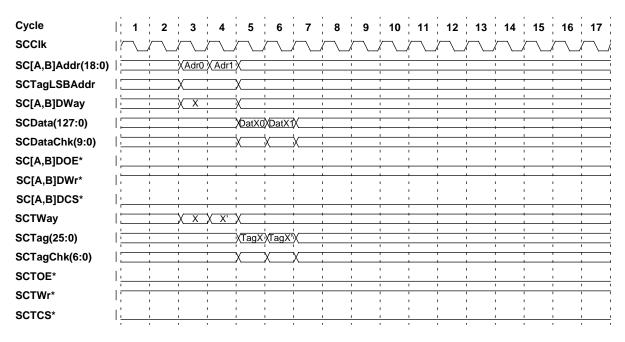

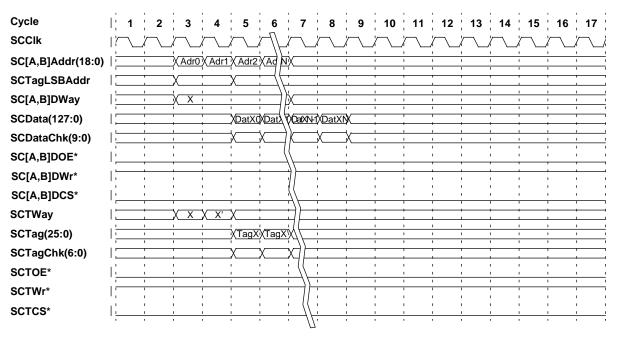

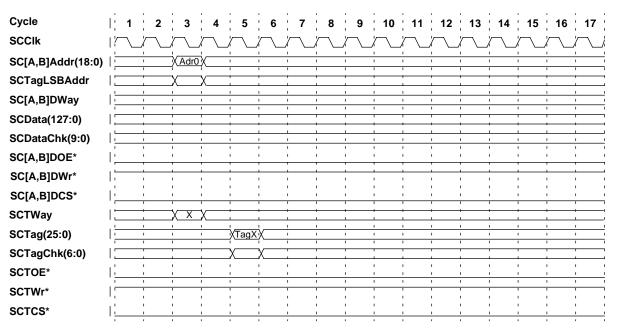

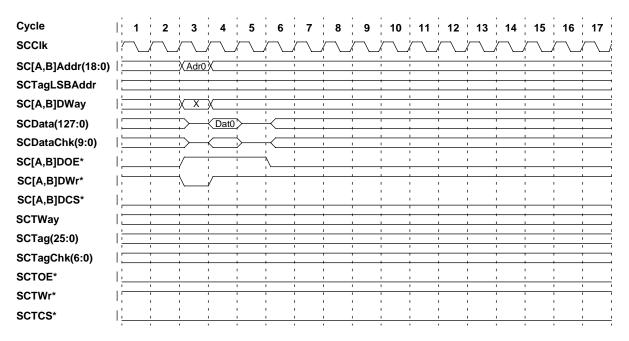

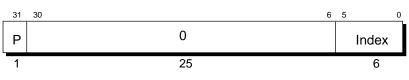

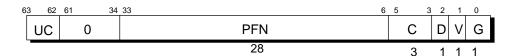

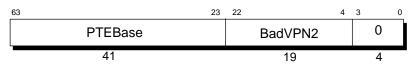

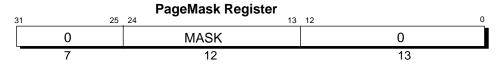

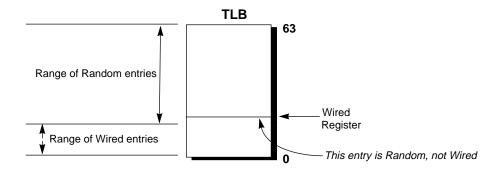

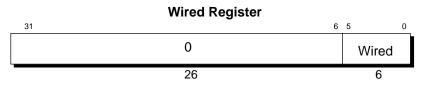

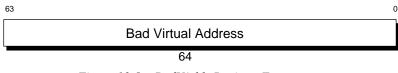

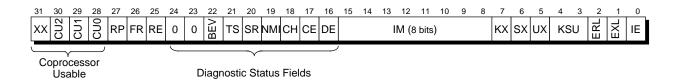

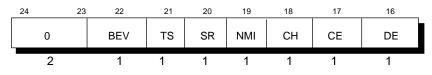

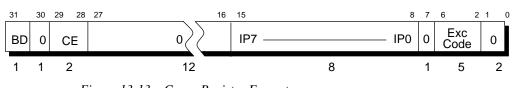

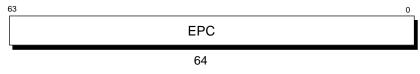

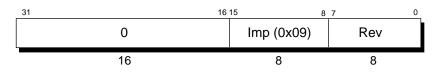

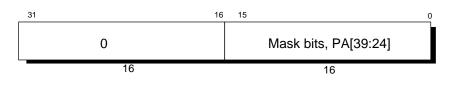

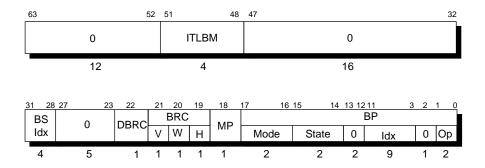

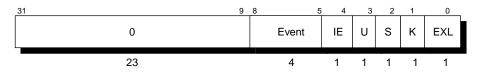

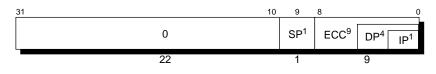

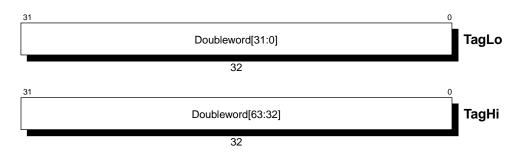

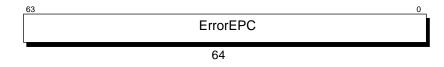

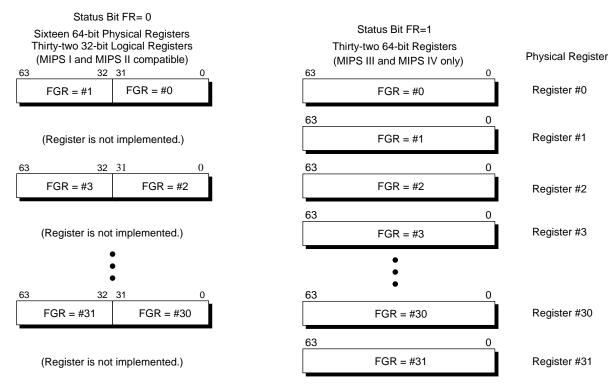

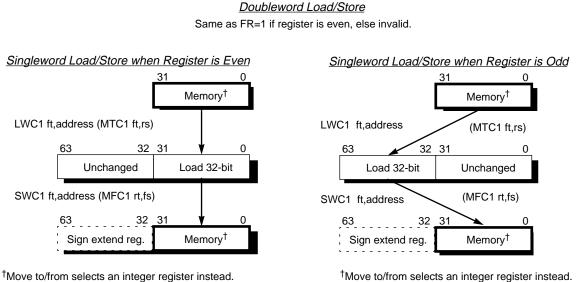

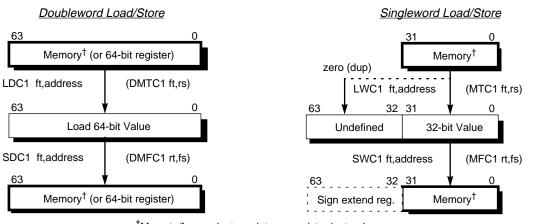

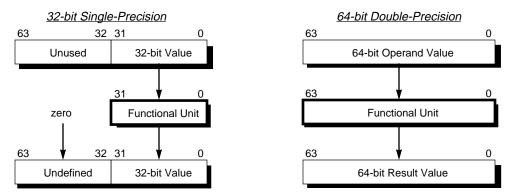

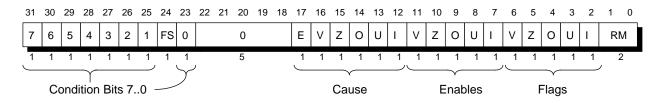

#### FP and Integer-Queue Issue Policy (R12000)