## **SP8703**

## 1GHz LOW CURRENT TWO-MODULUS DIVIDER

The SP8703 is a divide by 128/9 programmable divider with a maximum specified operating frequency of 1GHz. The signal (clock) inputs are biased internally and require to be capacitor coupled.

The output stage is CMOS compatible only, the 0 to 1 output edge giving best loop delay performance.

A unique 'power-down' feature is included to minimise power consumption

power consumption.

## **FEATURES**

- DC to 1GHz Operation

- -30° to +70°C Temperature Range

- Unique Power-Down Feature

- **CMOS** Compatible

# **ABSOLUTE MAXIMUM RATINGS**

**QUICK REFERENCE DATA** Supply Voltage 5.0V ± 0.25V Supply Current 30mA Typical

MODULUS CONTROL Vcc INPUT BIAS DECOUPLE OUTPUT INPUT DECOUPLE ( POWER DOWN MP8,DG8

Fig.1 Pin connections - top view

Supply voltage Storage temperature range Max. junction temperature Max. clock I/P voltage -30°C to +150°C +175°C 2.5V p-p

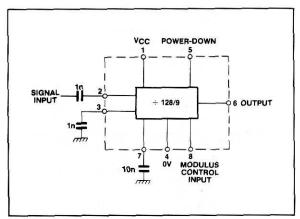

Fig.2 Functional diagram

## **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated): Vcc = +4.75V to 5.25V, Tamb = -30°C to +70°C

| Characteristics                                                                       | Value           |                  | Units             | Conditions                              | Notes                                  |

|---------------------------------------------------------------------------------------|-----------------|------------------|-------------------|-----------------------------------------|----------------------------------------|

|                                                                                       | Min.            | Max.             | Units             | Conditions                              | , 10103                                |

| Maximum frequency Maximum frequency                                                   | 1000<br>950     | 50               | MHz<br>MHz<br>MHz | T <sub>amb</sub> = 25°C                 | Note 1,2,4<br>Note 1,2,3<br>Note 1,2,3 |

| Minimum frequency (sinewave)  Power supply current  Power supply current              |                 | 40<br>3          | mA<br>mA          | Power-up<br>Power-down                  | Note 3<br>Note 3                       |

| Output high voltage Output low voltage                                                | 3.2<br>0        | Vcc<br>1.7       | V                 | IL = -0.2mA<br>IL = 0.2mA               | Note 3<br>Note 3                       |

| Control input high voltage<br>Control input low voltage<br>Control input high current | 3.2             | Vcc<br>1.7<br>50 | ν<br>ν<br>μΑ      | Divide by 128 Divide by 129 Input = Vcc | Note 3<br>Note 3<br>Note 3<br>Note 3   |

| Control input low current Power-down high voltage                                     | -10<br>3.2<br>0 | Vcc<br>1.7       | μA<br>V<br>V      | Input = 0V Power-down Power-up          | Note 3<br>Note 3                       |

| Power-down low voltage Power-down high current Power-down low current                 | -2              | 10               | μA<br>μA          | Input = Vcc<br>Input = 0V               | Note 3<br>Note 3                       |

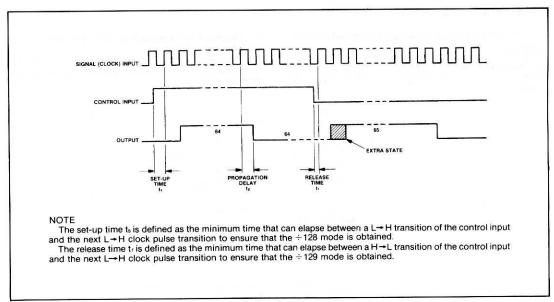

| Clock to output delay<br>Set-up time<br>Release time                                  |                 | 30<br>15<br>15   | ns<br>ns<br>ns    | CL = 10pF<br>CL = 10pF<br>CL = 10pF     | Note 5<br>Note 5<br>Note 5             |

- NOTES

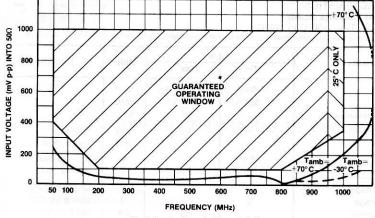

1. See Fig.4 for guaranteed operating window.

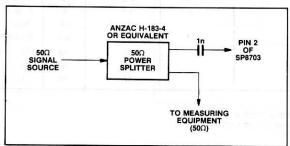

2. See Fig.5 for input voltage measurement method.

3. Tested at 25°C and +70°C only.

4. Tested at 25°C only.

5. Guaranteed but not tested.

Fig.3 Timing diagram

Fig.4 Typical input characteristics

Fig.5 Input voltage measurement method

### **OPERATING NOTES**

- 1. The inputs are biased internally and coupled to a signal source with suitable capacitors.

2. If no signal is present the devices will self-oscillate. If this

- is undesirable it may be prevented by connecting a 15k resistor from one input to pin 4 (ground). This will reduce the sensitivity.

\*Tested as specified

in table of Electrical Characteristics

The circuits will operate down to DC but slew rate must be better than 100V/µs.

The output stage is of an unusual design and is intended to interface with CMOS. External pull-up resistors or circuits must not be used.